# Low Frequency Noise and Gate Bias Instability in Normally-Off AlGaN/GaN HEMTs

Felice Crupi, Senior Member, IEEE, Paolo Magnone, Sebastiano Strangio, Ferdinando Iucolano, Gaudenzio Meneghesso, Fellow IEEE

Abstract — In this paper, traps-related dispersion phenomena are investigated on GaN/AlGaN MOS-HEMTs. Pulsed I-V characteristics and low-frequency-noise measurements are the characterization vehicles used to get a direct insight of the device trap-states. By considering a set of 10 samples, device-to-device fluctuation parameters extracted from trap-related measurements (1/f noise and gate bias instability) are systematically compared with conventional electrical parameters (threshold voltage and on-current). Two separate trends are identified and ascribed to two different trap families.

*Index Terms*— GaN, MOS-HEMT, traps, low frequency noise, gate bias instability, threshold voltage.

## I. INTRODUCTION

THE requirements of higher efficiency and higher power density in power electronics calls for performant switching devices, exhibiting low conduction losses and high operating frequency. In this field, GaN High Electron Mobility Transistor (HEMT) represents a valuable solution, because of the improved breakdown voltage/on-resistance trade-off, higher temperature capability and larger operating frequency, with respect to conventional Si-based devices. An important limitation of GaN devices is represented by current collapse phenomenon, leading to an increase of dynamic resistance when operating in switching conditions [1-4]. Recent studies [5-7] have demonstrated that traps responsible for current collapse are localized in the buffer layer. On the other hand, normally-off transistors are required for circuital applications, hence avoiding the adoption of complicated drive solutions (e.g. cascade solutions for the control of normally-on devices).

This work was supported in part by the ENIAC-324280 Energy Efficient Converters using GaN Power Devices (E2COGaN).

F. Crupi is with the Department of Computer Engineering, Modeling, Electronics and Systems Engineering, University of Calabria, Rende 87036, Italy (e-mail: felice.crupi@unical.it;).

P. Magnone is with the Department of Management and Engineering, University of Padua, I-36100 Vicenza, Italy (e-mail: paolo.magnone@unipd.it).

S. Strangio is with the Department of Electrical, Management and Mechanical Engineering, University of Udine, Udine 33100, Italy (seb88str@gmail.com).

F. Iucolano is with the STMicrolectronics, Stradale Primosole 50, Zona industriale, 95121 Catania, Italy (e-mail: ferdinando.iucolano@st.com).

G. Meneghesso is with the Department of Information Engineering, University of Padua, Padua 35131, Italy (e-mail: gaudenzio.meneghesso@dei.unipd.it).

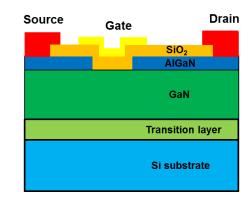

Fig. 1. Sketchof the AlGaN/GaN MOS-HEMT under investigation.

Among the different approaches to achieve normally-off devices, GaN-based hybrid MOS-HEMTs have been proposed [8]. In the case of MOS-HEMT or MIS-HEMT architectures, threshold voltage instability under gate bias stress have been proved to limit on- current and resistance [9-11].

Given the importance of trap distribution in GaN HEMTs, low-frequency noise (LFN) measurements represent a powerful tool for the analysis of these devices. This technique has been widely applied to the field of CMOS technology, in order to assess the defectiveness of materials and in particular of gate dielectric [12-15]. Recently, the validity of LFN measurements has been proved in the case of power semiconductor devices, such as power MOSFETs [16] or GaN HEMTs [17, 18].

In this paper, a study of LFN is performed on AlGaN/GaN MOS-HEMTs, aiming at understanding the distribution of defects in the structure. By conducting a correlation analysis among LFN, gate bias instability and conventional electrical parameters (threshold voltage and on-current), we are able to identify two types of defect.

## II. EXPERIMENTAL

HEMTs have been fabricated on AlGaN/GaN heterostructures grown on Si (111) substrates. The recessed approach has been used to obtain a normally-off device. A schematic cross section of the fabricated recessed hybrid MOS-HEMT structure is reported in Fig. 1. The ohmic contacts were formed by Ti/Al-based metallization, while Nibased were used for the gate contact. Details on the ohmic and gate contacts formation can be found in [19] and [20],

© 2016 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other users, including reprinting/ republishing this material for advertising or promotional purposes, creating new collective works for resale or redistribution to servers or lists, or reuse of any copyrighted components of this work in other works. DOI: 10.1109/TED.2016.2544798 - © 2016 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See <a href="http://www.ieee.org/publications\_standards/publications/rights/index.html">http://www.ieee.org/publications\_standards/publications/rights/index.html</a> for more information.

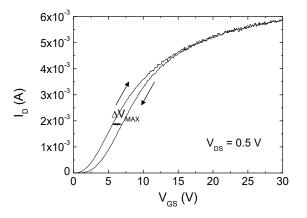

Fig. 2. Drain current as function of pulsed gate voltage. The hysteresis observed in the I-V curve is quantified by evaluating the maximum gate voltage shift  $\Delta V_{MAX}$  for different I<sub>D</sub> values.

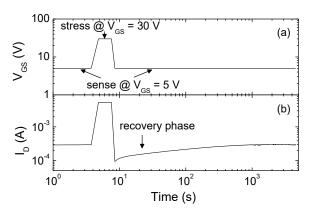

Fig. 3. Drain current dynamics after applying a positive voltage stress. The device exhibits a recovery time in the order of minutes.

respectively. The AlGaN layer was recessed using a dry etch process in a chlorine-based chemistry. As gate insulator,  $SiO_2$  layer (50 nm thick) was deposited by plasma enhanced chemical vapour deposition using tetraethyl orthosilicate (TEOS) precursor, and subjected to a thermal annealing at  $850^{\circ}C$  in N<sub>2</sub>.

We used two different types of electrical characterization techniques, LFN and pulsed I-V. LFN measurements were performed by using a purposely designed measurement system, consisting of two low noise bias stages (for the gate and the drain terminal) and a low noise trans-impedance amplifier [14, 16]. Noise data were acquired by biasing the devices in linear regime with  $V_{DS} = 500$  mV. Pulsed I-V measurements were carried out by means of a parameter analyzer Keithley 4200-SCS equipped with the 4225-PMU ultra fast I-V module and two 4225-RPM remote amplifier/switch modules. I-V curves were obtained by applying a train of pulses with a period of 300 µs and a width of 30 µs at the gate and drain terminals. The gate voltage pulse amplitude was varied from 0 to 30 V with a step of 100 mV, while the drain voltage pulse amplitude was kept constant at 500 mV. Overall, the time required to sweep  $V_{GS}$  from 0 V up to 30 V is 90 ms, while the effective stress time is 9 ms. In order to perform a correlation analysis on different device

electrical parameters, experiments are carried out on a set of 10 samples.

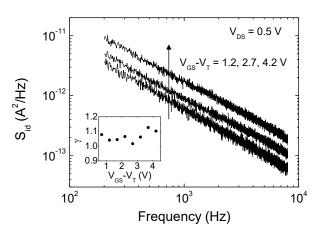

Fig. 4. Power spectral density of the drain current noise. Typical flicker 1/f' noise is observed. As reported in the inset,  $\gamma$  values are very close to 1.

#### III. RESULTS AND DISCUSSION

A typical pulsed  $I_D$ -V<sub>GS</sub> curve of a normally-off GaN HEMT is reported in Fig. 2. Even if the pulse time is reduced down to 30µs, a significant hysteresis is observed on the I-V curve when sweeping V<sub>GS</sub> from 0 V up to 30 V and then down to 0 V again. As observed in [9-11], the reduction of current can be ascribed to traps located at the oxide/GaN interface or in the lateral regions, leading to a change of the threshold voltage. In order to quantify the hysteresis in the I-V curve, we measured the maximum voltage shift  $\Delta V_{MAX}$  as reported in Fig. 2. The dynamics of drain current, following a gate voltage stress (30 V for xx s), is reported in Fig. 3. The recovery phase, required in order to bring the drain current level back to the initial value, is in the order of minutes. Hence, traps involved during forward bias stress show a highly asymmetric trapping and detrapping time.

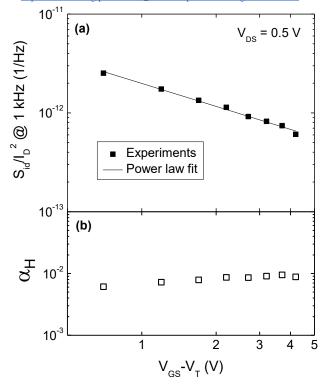

The power spectral density (PSD) of the drain current is reported in Fig. 4 for different gate voltage overdrive (VGS-V<sub>Th</sub>). It is worth noting that noise measurements were carried out in fresh devices under stationary conditions. As shown in the inset,  $1/f^{\gamma}$  noise, with  $\gamma$  very close to 1, is observed for all the considered bias conditions. The normalized drain current spectra are then plotted against the gate voltage overdrive in Fig. 5a. Experimental data are fitted with the function  $S_{ID}/I_D^2 \propto |V_{GS}-V_T|^{\alpha}$ . The slope  $\alpha$  of this plot gives information about the fundamental fluctuation mechanism [14]. In particular, being the slope close to -1, mobility fluctuation can be assumed as the source of fluctuation for the drain current. In this case, it is well known that defects responsible for the1/f noise are physically located in the gate dielectric. Moreover, 1/f noise arising from source and drain series- resistance can be assumed negligible, since a normalized noise independent of the bias point would be expected for this case [21]. As a result we can assert that 1/f noise is mainly related to traps located in the gate region. In particular, both gate dielectric quality and SiO<sub>2</sub>/GaN interfacial defects (due to plasma deposition) could be responsible for the 1/f noise.

© 2016 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other users, including reprinting/ republishing this material for advertising or promotional purposes, creating new collective works for resale or redistribution to servers or lists, or reuse of any copyrighted components of this work in other works. DOI: 10.1109/TED.2016.2544798 - © 2016 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See <a href="http://www.ieee.org/publications/rights/index.html">http://www.ieee.org/publications/rights/index.html</a> for more information.

Fig. 5. (a) Normalized  $S_{id}$  as a function of gate voltage overdrive. Being the slope  $\alpha$  close to -1 (and in particular equal to -0.8), mobility fluctuation can be assumed as the source of flicker noise. (b) Hooge parameter ( $\alpha_{H}$ ) calculated according to the mobility fluctuation model [14]. The Hooge parameter is larger than what typically observed in silicon-based MOS devices (10<sup>-3</sup>).

According to the mobility fluctuation model, the so-called Hooge parameter can be estimated [14], representing a figure of merit of the MOS quality. In Fig. 5b we can observe that, the value obtained for AlGaN/GaN MOS-HEMTs is significantly larger than what typically found in MOSFET devices (in the order of  $10^{-3}$ ) [14], pointing out a relevant defectiveness of SiO<sub>2</sub>/GaN interface.

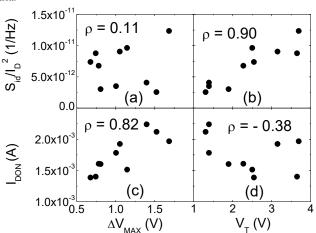

In Fig. 6 we report correlation plots among the following parameters: i) normalized flicker noise  $S_{ID}/I_D^2$  at f = 1kHz and  $I_D = 300 \ \mu A$ ; ii) gate voltage shift  $\Delta V_{MAX}$  due threshold voltage instability; iii) threshold voltage V<sub>T</sub> in fresh devices; iv) drain current I<sub>DON</sub> at fixed gate voltage overdrive (V<sub>GS</sub> - V<sub>T</sub> = 5V) in fresh devices. As shown in Fig. 6a,  $S_{ID}/I_D^2$  and  $\Delta V_{MAX}$  are basically uncorrelated parameters. This means that 1/f drain current fluctuations and gate bias instability phenomenon origin from different defects. Since LFN measurements are performed at low gate voltage, we can assume negligible degradation occurs in the device. Therefore, noise is mainly related to defects in the fresh device. On the other hand, when considering a large gate bias stress (as in the case of  $\Delta V_{MAX}$  measurement), a significant number of charges can be trapped close to the SiO2/GaN interface. The experimental uncorrelation points out that the amount of V<sub>T</sub> instability is not related to the initial LFN and to traps affecting the transport at low gate voltage. Different scenarios then possible for are the

Fig. 6. Correlation plots:  $S_{id}/I_D^2 vs. \Delta V_{MAX}$  (a),  $S_{id}/I_D^2 vs. V_T$  (b),  $I_{DON} vs. \Delta V_{MAX}$  (c) and  $I_{DON} vs. V_T$  (d). Strong correlation is observed between the drain current noise and threshold voltage (b) and between gate voltage shift and on-current (c).

traps involved during gate bias stress: i) could be those in the lateral regions (as suggested in [10]); ii) could be those under the gate region but having different energy with respect to those involved in LFN analysis; iii) new defects could be generated during the stress. Considering the complete recovery observed in Fig. 3, the hypothesis of generation of new defects is hardly plausible.

Given the amount of cumulative stress time received by the samples (18 ms during the sweep in both directions), the measured  $\Delta V_{MAX}$  (in the order of 1V) is significantly large. In fact, Guo et al. [9] reported that in a MOS-HEMT with 50nm of SiO<sub>2</sub> oxide, a gate voltage stress of 15V must be applied for about 10<sup>4</sup> s in order to obtain a comparable degradation. Moreover, as opposite to our case, a significant permanent degradation was observed.

As reported in Fig. 6b, 1/f noise is strongly correlated with the device threshold voltage. Therefore, the significant threshold voltage variability can be ascribed to the defects in gate dielectric or at the SiO<sub>2</sub>/GaN interface, affecting the work-function of the MOS structure. In Fig. 6c, a strong correlation between  $\Delta V_{MAX}$  and I<sub>DON</sub> is observed, meaning that devices exhibiting larger drain current are subject to a larger threshold voltage instability. Moreover, according to Fig. 6d, the variation of on-current cannot be ascribed to the initial threshold voltage, since a weak correlation is observed.

### IV. CONCLUSIONS

In this paper, we analyzed 1/f drain current noise along with threshold voltage instability effects in AlGaN/GaN MOS-HEMTs. The low frequency noise analysis pointed outa 1/f trend on mobility fluctuation basis, characterized by a Hooge parameter close to 10<sup>-2</sup>. This relatively large value can be ascribed to the defectiveness of SiO<sub>2</sub>/GaN interface. These defects are also responsible for therelevant dispersion of the threshold voltage in fresh devices. On the other hand, the correlation analysis highlighted that threshold voltage instability seems to be related to different defects, perhaps having different energy or localized in the lateral regions.

© 2016 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other users, including reprinting/ republishing this material for advertising or 4 promotional purposes, creating new collective works for resale or redistribution to servers or lists, or reuse of any copyrighted components of this work in other works. DOI: 10.1109/TED.2016.2544798 - © 2016 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See <a href="http://www.ieee.org/publications\_standards/publications/rights/index.html">http://www.ieee.org/publications/rights/index.html</a> for more information.

Furthermore, samples exhibiting a larger threshold voltage

instability also show a larger on-current, even if the current level is uncorrelated with the initial threshold voltage.

#### REFERENCES

- J. Donghyun, and J. A. Del Alamo, "Methodology for the study of dynamic ON-resistance in high-voltage GaN field-effect transistors", *IEEE Trans. Electron Devices*, vol. 60, no. 10, pp. 3190-3196, Oct. 2013. DOI: 10.1109/TED.2013.2274477

- [2] A. Tarakji, G. Simin, N. Ilinskaya, X. Hu, A. Kumar, A. Koudymov, J. Yang, M. Asif Khan, M. S. Shur, and R. Gaska "Mechanism of radio-frequency current collapse in GaN–AlGaN field-effect transistors", *Appl. Phys. Lett.*, vol. 78, no. 15, pp. 2169-2171, Apr. 2001. DOI: 10.1063/1.1363694

- [3] T. Mizutani, Y. Ohno, S. Kishimoto, and K. Maezawa, "A study on current collapse in AlGaN/GaN HEMTs induced by bias stress", *IEEE Trans. Electron Devices*, vol. 50, no. 10, pp. 2015-2020, Oct. 2003. DOI: 10.1109/TED.2003.816549

- [4] R. Chu, A. Corrion, M. Chen, R. Li, D. Wong, D. Zehnder, B. Hughes, and K. Boutros, "1200-V normally off GaN-on-Si field-effect transistors with low dynamic ON-resistance", *IEEE Electron Device Lett.*, vol. 32, no. 5, pp. 632-634, May 2011. DOI: 10.1109/LED.2011.2118190

- [5] M. Meneghini, I. Rossetto, D. Bisi, A. Stocco, A. Cester, G. Meneghesso, E. Zanoni, A. Chini, A. Pantellini, and C. Lanzieri, "Role of buffer doping and pre-existing trap states in the current collapse and degradation of AlGaN/GaN HEMTs", *Proc. IEEE IRPS*, Jun. 2014, pp. 6C.6.1-6C.6.7. DOI: 10.1109/IRPS.2014.6861113

- [6] M. Wang, D. Yan, C. Zhang, B. Xie, C. P. Wen, J. Wang, Y. Hao, W. Wu, and B. Shen, , "Investigation of surface- and buffer-induced current collapse in GaN high-electron mobility transistors using a soft switched pulsed I–V measurement", *IEEE Electron Device Lett.*, vol. 35, no. 11, pp. 1094-1096, Nov. 2014. DOI: 10.1109/LED.2014.2356720

- [7] M. J. Uren, J. Moreke, and M. Kuball, "Buffer design to minimize current collapse in GaN/AlGaN HFETs", *IEEE Trans. Electron Devices*, vol. 59, no. 12, pp. 3327-3333, Dec. 2012. DOI: 10.1109/TED.2012.2216535

- [8] P. Fiorenza, G. Greco, F. Iucolano, A. Patti, and F. Roccaforte, "Slow and fast traps in metal-oxide-semiconductor capacitors fabricated on recessed AlGaN/GaN heterostructures", *Appl. Phys. Lett.*, vol. 106, no. 14, pp. 142903-1-142903-4, Apr. 2015. DOI: 10.1063/1.4917250

- [9] A. Guo, and J. A. del AlamoPositive-Bias Temperature Instability (PBTI) of GaN MOSFETs", *Proc. IEEE IRPS*, pp. 6C.5.1 - 6C.5.7, April 2015. DOI: 10.1109/IRPS.2015.7112770

- [10] P Lagger, C. Ostermaier, G. Pobegen, and D. Pogany, "Towards Understanding the Origin of Threshold Voltage Instability of AlGaN/GaN MIS-HEMTs", *Proc. IEEE IEDM*, pp. 13.1.1 - 13.1.4, Dec. 2012. DOI: 10.1109/IEDM.2012.6479033

- [11] S. Yang, Y. Lu, H. Wang, S. Liu, C. Liu, and K. J. Chen, "Dynamic Gate Stress-Induced VTH Shift and Its Impact on Dynamic RON in GaN MIS-HEMTs", *IEEE Electron Device Lett.*, vol. 37, no. 2, pp. 157-160, Feb. 2016. DOI: 10.1109/LED.2015.2505334

- [12] E. Simoen, and C. Claeys, "On the flicker noise in submicron silicon MOSFETs", *Solid-State Electron.*, vol. 43, no. 5, pp. 865-882, May 1999. DOI: 10.1016/S0038-1101(98)00322-0

- [13] G. Ghibaudo, and T. Boutchacha, "Electrical noise and RTS fluctuations in advanced CMOS devices", *Microelectron. Reliab.*, vol. 42, no. 4-5, pp. 573–582, Apr.-May 2002. DOI: 10.1016/S0026-2714(02)00025-2

- [14] P. Magnone, F. Crupi, G. Giusi, C. Pace, E. Simoen, C. Claeys, L. Pantisano, D. Maji, V. R. Rao, and P. Srinivasan, "1/f Noise in drain and gate current of MOSFETs with high-k gate stacks", *IEEE Trans. Device Mater. Rel.*, vol. 9, no. 2, pp. 180-189, Jun. 2009, DOI: 10.1109/TDMR.2009.2020406

- [15] F. Crupi, G. Giusi, G. Iannaccone, P. Magnone, C. Pace, E. Simoen, and C. Claeys, "Analytical model for the 1/f noise in the tunneling current through metal-oxide-semiconductor structures", *J. Appl. Phys.*, vol. 106, no. 7, pp. 073710-1-073710-6, Oct. 2009. DOI: 10.1063/1.3236637

- [16] P. Magnone, P. A. Traverso, G. Barletta, and C. Fiegna, "Experimental characterization of low-frequency noise in power MOSFETs for defectiveness modelling and technology assessment", *Measurement*, vol. 52, no. 1, pp. 47-54, Jun 2014. DOI: 10.1016/j.measurement.2014.02.033

- [17] H.-C. Chiu, J.-H. Wu, C.-W. Yang, F.-H. Huang, and H.-L. Kao, "Lowfrequency noise in enhancement-mode GaN MOS-HEMTs by using

stacked Al<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub>/Gd<sub>2</sub>O<sub>3</sub> gate dielectric", *IEEE Electron Device Lett.*, vol. 33, no. 7, pp. 958-960, Jul. 2012. DOI: 10.1109/LED.2012.2194980

- [18] T. Roy, E. X. Zhang, Y. S. Puzyrev, D. M. Fleetwood, R. D. Schrimpf, B. K. Choi, A. B. Hmelo, and S. T. Pantelides, "Process dependence of proton-induced degradation in GaN HEMTs", *IEEE Trans. Nucl. Sci*, vol. 57, no. 6, pp. 3060-3065, Dec. 2010. DOI: 10.1109/TNS.2010.2073720

- [19] F. Iucolano, G. Greco, and F. Roccaforte, "Correlation between microstructure and temperature dependent electrical behavior of annealed Ti/Al/Ni/Au Ohmic contacts to AlGaN/GaN heterostructures", *Appl. Phys. Lett.*, vol. 103, no. 20, pp. 201604-1-201604-4, Nov. 2013. DOI: 10.1063/1.4828839

- [20] F. Iucolano, C. Miccoli, M. Nicotra, A. Stocco, F. Rampazzo, A. Zanandrea, Cinnera V. Martino, A. Patti, S. Rinaudo, F. Soci, A. Chini, E. Zanoni, and G. Meneghesso, "Influence of properties of Si3N4 passivation layer on the electrical characteristics of Normally-off AlGaN/GaN HEMT", *IEEE WiPDA*, Oct. 2013, pp. 162-165. DOI: 10.1109/WiPDA.2013.6695587

- [21] E. Vandamme, L. K. J. Vandamme, E. Simoen, R. Schreutelkamp, and C. Claeys, "Impact of silicidation on the excess noise behaviour of mos transistors", *Solid State Electron.*, vol. 38, no. 11, pp. 1893–1897, Nov. 1995. DOI: 10.1016/0038-1101(95)00011-H