# Assessment of InAs/AlGaSb Tunnel-FET Virtual Technology Platform for Low-Power Digital Circuits

Sebastiano Strangio, Pierpaolo Palestri, Senior Member, IEEE, Marco Lanuzza, Member, IEEE, Felice Crupi, Senior Member, IEEE, David Esseni, Fellow, IEEE, Luca Selmi, Fellow, IEEE

*Abstract* — In this work, a complementary InAs/Al<sub>0.05</sub>Ga<sub>0.95</sub>Sb tunnel field-effect-transistor (TFET) virtual technology platform is benchmarked against the projection to the CMOS FinFET 10-nm node, by means of device and basic circuit simulations. The comparison is performed in the ultra-low voltage regime (below 500 mV), where the proposed III-V TFETs feature on-current levels comparable with scaled FinFETs, for the same low-operating-power (LOP) off-current. Due to the asymmetrical n-and p-type I-Vs, trends of noise margins and performances are investigated for different Wp/Wn ratios. Implications of the device threshold voltage variability, which turned out to be dramatic for steep slope TFETs, are also addressed.

#### Index Terms-TFET, VLSI, III-V, Full-Adder.

# I. INTRODUCTION

THE growing need for energy efficient electronics is calling for alternative device concepts, based on different operating principles and semiconductor materials with respect to the conventional silicon MOSFET. The tunnel field-effecttransistor (TFET) realized with III-V broken-gap/staggered heterostructures represents an interesting option due to its potential sub-60 mV/dec operation at suitable current levels [1-8]. Some experimental InAs/GaSb TFETs have already shown evidence of a relatively high on-current for reduced supply voltage (>100  $\mu$ A/ $\mu$ m for V<sub>DD</sub> = 500 mV) [6-8], whereas the reported sub-threshold swing (SS) levels are still unattractive due to detrimental aspects related to the immaturity of the fabrication process [9-11]. Considering that atomistic full-quantum simulators can dependably predict the quantum effects underlying the TFET operation, sophisticated numerical simulations are widely used, as a cost effective alternative to device fabrication and characterization, in order to scrutinize the most suitable heterostructure materials and to optimize the key design parameters. In this context, a virtual TFET technology platform consisting of InAs/Al<sub>0.05</sub>Ga<sub>0.95</sub>Sb nanowires has been recently designed by *Baravelli et al.* [1-2].

The assessment of a technology can be carried out by evaluating device-level figures-of-merit (on- and off- currents for a certain  $V_{DD}$ , SS, intrinsic capacitances, etc.), which can be translated trough simplified models in circuit performances. A preliminary benchmark against the projections to the 10-nm node for CMOS FinFETs (i.e. the *predictive technology models for the 10-nm node multi gate transistors* [12,13]) has been already shown in [2]. The comparison was carried out by considering the static and dynamic behavior of an inverter, as obtained from a post-processing of the drain current characteristics and effective gate capacitance of the p- and n-type TFETs (T<sub>P</sub> and T<sub>N</sub>, respectively).

On the other hand, a comparison with conventional CMOS transistors, whose different operating mechanism leads to different I-Vs and C-Vs trends, can lead to questionable conclusions if based exclusively on figures-of-merit for devices and/or inverters. A more systematic benchmark should include a circuit-level analysis with the evaluation of related static and dynamic figures-of-merit [14-19]. To this purpose, basic logic circuits such as inverters and ring-oscillators are employed in this work to investigate the effects of the p-/ntype device asymmetry and to identify the best  $W_P/W_N$  ratio. Then, the conventional 28T full-adder, identified as a relevant vehicle circuit representative of the digital logic environment, is analyzed in detail; performance and energy figures-of-merit, extracted for both TFET and FinFET implementations, are compared and discussed. Furthermore, the implications of device-to-device process variations are also considered, since they become a major concern in the ultra-low voltage scenario.

The reminder of this paper is organized as follows. Section II describes the simulation approach along with the calibration of the device models against full-quantum simulations; the simulation methodology for the digital circuits is presented too. Section III presents preliminary TFET simulations based on simple circuits, to address the p-/n-type device imbalance and to find a suitable  $W_P/W_N$  ratio. In Section IV, the simulation results on full-adders are presented along with the  $V_{\rm th}$  variability effects. Finally, Section V concludes the paper.

## II. SIMULATION METHODOLOGY

The simulation analysis has been carried out within the *Cadence* environment, by employing for the TFETs Verilog-A

Manuscript received March 8, 2016. The research leading to these results has received funding from the European Community's Seventh Framework Programme under grant agreement No. 619509 (project E2SWITCH).

S. Strangio, P. Palestri, D. Esseni and L. Selmi are with the DPIA (Dipartimento Politecnico di Ingegneria e Architettura), Università degli Studi di Udine, Via delle Scienze 206, 33100 Udine, Italy (e-mail: seb88str@gmail.com, pierpaolo.palestri@uniud.it, david.esseni@uniud.it, luca.selmi@uniud.it).

M. Lanuzza and F. Crupi are with the DIMES (Dipartimento di Ingegneria Informatica, Modellistica, Elettronica e Sistemistica), Università della Calabria, Rende 87036, Italy (e-mail: lanuzza@dimes.unical.it, felice.crupi@unical.it).

(c) 2016 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other users, including reprinting/ republishing this material for advertising or promotional purposes, creating new collective works for resale or redistribution to servers or lists, or reuse of any copyrighted components of this work in other works. DOI: 10.1109/TED.2016.2566614 - © 2016 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

compact models based on lookup tables (LUTs) with the device characteristics predicted by the full-quantum simulator [1,2]. Differently, -spice models [12,13] for the FinFETs were used. In the procedure for generating the LUTs, the drain current I<sub>D</sub> and the gate capacitances (C<sub>GS</sub> and C<sub>GD</sub>) need to be computed for each biasing point of a discretized bidimensional domain represented by the V<sub>GS</sub> and V<sub>DS</sub> variables, where the widths of the  $\Delta V_{GS}$  and  $\Delta V_{DS}$  steps determine the tradeoff between computation burden and accuracy. In order to improve the computational efficiency in the generation of the I<sub>D</sub>-V<sub>GS</sub>-V<sub>DS</sub>, C<sub>GS</sub>-V<sub>DS</sub> and C<sub>GD</sub>-V<sub>GS</sub>-V<sub>DS</sub> LUTs and with marginal accuracy losses (voltage steps of 10 mV), we have used the TCAD simulator Sentaurus Device (*sdevice*) [20] to reproduce the results from [1,2] through a fine calibration of the TCAD models, as described below.

# *A.* TCAD model calibration and Verilog-A compact model verification

The complementary InAs/AlGaSb TFETs proposed in [1,2] feature a 20 nm gate-length, a  $7 \times 7$  nm<sup>2</sup> square cross-section and an EOT of 1 nm. The TFET design consisted in the careful selection of several key-aspects, such as the nanowire geometry (cross-section and source-gate-drain length), the material parameters (i.e. the Al mole fraction in the AlGaSb), and the doping levels. These parameters play a key-role in the device electrical behavior, since all of them affect the heterostructure band-diagram lineup, which is clearly crucial for the band-to-band-tunneling (BtBT) mechanism.

TCAD models have been recalibrated in order to fit the  $T_P$  and  $T_N$  transfer-characteristics of the full-quantum results, as reported in Fig.1a. Although such calibration was performed just by focusing on the I<sub>D</sub>-V<sub>GS</sub>, the agreement between the TCAD simulations and the data from [2] is also satisfactory for the output-characteristics (I<sub>D</sub>-V<sub>DS</sub>) and gate capacitance characteristics (C<sub>GG</sub>-V<sub>GS</sub>), as evidenced in Fig.1b ( $T_P$  and  $T_N$  I<sub>D</sub>-V<sub>DS</sub>) and in Fig.1c-d (C<sub>GG</sub> of  $T_P$  and of  $T_N$ , respectively).

The calibration<sup>1</sup> was conducted in the following steps: (1) matching of the InAs/Al<sub>0.05</sub>Ga<sub>0.95</sub>Sb heterostructure band diagram, by adjusting the energy gap (E<sub>G</sub>) and the electron affinity ( $\chi$ ) to take into account for the effects of size-induced quantization [1], (2) calculation of the A<sup>direct</sup> and B<sup>direct</sup> constants for the dynamic nonlocal-path BtBT model [20] from the effective masses of bulk InAs and GaSb [21], (3) trimming of the effective valence/conduction band density of states (N<sub>V</sub> and N<sub>C</sub>) to improve the match (that is reasonable since the corresponding effective density of states under quantization is larger than in the bulk case for semiconductors with strongly non-parabolic energy dispersion).

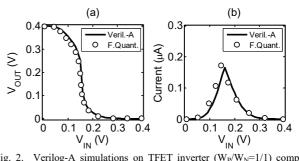

Fig.2 compares the voltage-transfer-characteristics (VTC) of a TFET inverter and the switching current as a function of the input voltage simulated in Verilog-A with the one reported in [2], which have been calculated with the load-line method by using the  $T_P$  and  $T_N$  device output characteristics from the full-

Fig. 1. Calibrated TCAD simulations (lines) compared with the ones simulated by means of the full-quantum simulator (symbols) [2]: (a)  $T_P$  and  $T_N$  transfer-characteristics at  $|V_{\rm DS}| = 400$  mV, (b)  $T_P$  and  $T_N$  output-characteristics at  $|V_{\rm GS}| = 400$  mV, (c)  $T_P$  and (d)  $T_N$  gate capacitance characteristics as a function of  $V_{\rm GS}$  at  $|V_{\rm DS}| = 0$  V and  $|V_{\rm DS}| = 0.4$  V.

Fig. 2. Verilog-A simulations on TFET inverter  $(W_P/W_N=1/1)$  compared with data extracted from full-quantum simulations [2]: (a) voltage transfer characteristics and (b) inverter switching current.  $V_{DD} = 400 \text{mV}$ .

quantum simulator. The good matching confirms the validity of our calibration and the effectiveness of the used Verilog-A model at the same time.

### B. Threshold voltage variability

Device-to-device variability is one of the major issues for circuits operating in the sub-threshold voltage regime. From the conventional MOSFET point of view, the various variability sources can be modeled together, considering that their combined effect leads to a variability of the threshold voltage  $V_{th}$  (VtV). The statistical variation of the FinFETs  $V_{th}$  can be estimated through the Pelgrom law [22], which relates the standard deviation of the  $V_{th}$  to the square root of the effective gate area of the device<sup>2</sup>. Concerning to TFETs, although a few theoretical studies have included the various process variation sources by means of statistical simulations at device level (including random dopant fluctuations (RDF), line

$<sup>^1</sup>$  Al\_{0.05}Ga\_{0.95}Sb (InAs) calibrated parameters: BtBT model: A =  $1.51\cdot 10^{20}$  (1.44  $\cdot 10^{20}$ ) cm $^{-3}s^{-1}$ , B = 9.54 (2.94) MV/cm. Effective density-of-states:  $N_C$  =  $1.26\cdot 10^{18}$  (5.22  $\cdot 10^{17}$ ) cm $^{-3}$ ,  $N_V$  =  $1.8\cdot 10^{19}$  (6.6  $\cdot 10^{18}$ ) cm $^{-3}$ .

$<sup>^{2}\</sup>sigma_{Vth} = A_{Vt} \cdot (W_{G,eff} \cdot L_{G})^{-1/2}$

(c) 2016 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other users, including reprinting/ republishing this material for advertising or promotional purposes, creating new collective works for resale or redistribution to servers or lists, or reuse of any copyrighted components of this work in other works. DOI: 10.1109/TED.2016.2566614 - © 2016 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

Fig. 3. Transfer-characteristics considering the V<sub>th</sub> variability (VtV) of the (a) T<sub>P</sub>, (b) T<sub>N</sub>, (c) M<sub>P</sub> and (d) M<sub>N</sub>. Compared to curves in Fig. 1a, the nominal V<sub>off</sub> (V<sub>GS</sub> @ I<sub>off,target</sub> = 35pA) of the n(p)-type devices (i.e. without VtV) are preventively increased (decreased): V<sub>off</sub>(T<sub>P</sub>) = -37 mV, V<sub>off</sub>(T<sub>N</sub>) = 45 mV, V<sub>off</sub>(M<sub>P</sub>) = -20 mV, V<sub>off</sub>(M<sub>N</sub>) = 20 mV, resulting in lower nominal I<sub>off</sub> (I<sub>D</sub> at V<sub>GS</sub> = 0 V and |V<sub>DS</sub>| = 400 mV). This V<sub>off</sub> setup ensures an average I<sub>off</sub> coinciding with the I<sub>off,target</sub> when VtV is activated.

edge roughness (LER) and metal gate work-function variation (VFV)) [23-28], due the poor maturity of the TFET technology, the estimate of the device sensitivity obtained either by simulations or by experimental data is similarly impractical. For this reason, we have simply assumed the same V<sub>th</sub> variability for both TFETs and FinFETs, which ensures a fair comparison between the two devices when performing the variability analysis at circuit level. In circuit simulations, the VtV has been modeled by adding a random voltage generator (with zero mean value) in series with the gate of each device, whose standard deviation is set to 35 mV (estimated for the FinFET architecture from <sup>(2)</sup>, assuming  $A_{vt} = 0.95 \text{ mV} \cdot \mu \text{m}$ [16,29,30]). It is worth mentioning that the same VtV affects the FinFETs and TFETs transfer-characteristics in a different way, due to their different shapes. The different SS (and g<sub>m</sub>/I<sub>D</sub>) of TFETs and FinFETs leads to a different sensitivity of the leakage [18] against a horizontal shift of the I<sub>D</sub>-V<sub>GS</sub>, which is a dramatic concern for TFETs due to their steeper characteristics at current levels close to Ioff. In Fig.3, the transfer-characteristics of the four devices under investigation are shown (M<sub>P</sub> and M<sub>N</sub> are the p- and n-type FinFET, respectively). Each figure shows the nominal curve (black solid line), the curves obtained from 1000 Monte-Carlo (MC) simulations by considering the VtV (grey lines) and the corresponding average value (dashed black line). In order to perform a comparison for similar leakage power, the nominal transfer characteristics (i.e. before activating the VtV), has been realigned so that the average value ( $\mu$ ) of the I<sub>off</sub> in

Fig. 4. (a) TFET and (b) FinFET inverter VTCs, for  $W_P/W_N=1/1$ : nominal simulation (black line) and 1000 MC simulations (grey lines). (c) TFET inverter and (d) FinFET inverter variability of the VTC maximum gain (both for  $W_P/W_N=1/1$ ). (e) TFET inverter noise margins (NMH and NML) as function of the  $W_P/W_N$  ratio (the ones of the FinFET inverter for  $W_P/W_N=1/1$  are reported too -red symbols-).  $V_{DD} = 400$ mV.

presence of VtV is the same for all the devices, that is  $\mu(I_{off}) = 35 \text{ pA}$  at  $V_{DD} = 400 \text{mV}$ , as shown in Fig.3.

# III. $W_P/W_N$ Sizing

Unlike the  $M_P$  and  $M_N$  FinFETs, which are essentially symmetric, the  $T_P$  and  $T_N$  TFETs feature asymmetric characteristics, given that the on-current is approximately 4 times larger for the  $T_N$  at  $V_{DD} = 400$  mV for a given transistor size. This explains the asymmetric TFET inverter VTC in Fig. 4a, as opposed to the FinFET one that is mirrored with respect to the line  $V_{OUT} = V_{IN}$ , with a logic threshold at  $V_{DD}/2$ . For this reason, inverter-based circuits are studied in this section with focus on noise margins, performance and energy trade-offs for various  $W_P/W_N$  conditions.

#### A. Static noise margins

In Fig.4a-b, the VTCs obtained for 1000 MC instances are reported along with the nominal cases. They result in the probability density function (PDF) in Fig.4c-d, consisting of the values of the maximum voltage gain for the TFET and FinFET inverter at the logic threshold, respectively, and for  $W_P/W_N = 1/1$ . The TFET inverter features a larger gain ( $\mu$ =58.43,  $\sigma$ =17.32), but also a larger variability than the FinFET one ( $\mu$ =12.43,  $\sigma$ =0.15). This difference can be understood by considering the nominal VTCs in Fig.4a and b: for the TFET inverter, the transition from the high- to the low-state is very sharp only close to the logic threshold; this is not the case of the FinFET inverter, where the slope of the V<sub>OUT</sub> (V<sub>IN</sub>) curve is almost constant in the whole transition but relatively lower. Despite the larger gain, the noise margins

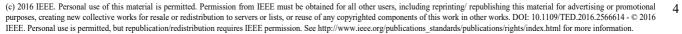

Fig. 5. Inverter-based blocks investigated used for the optimization of the  $T_P/T_N$  sizing: (a) self-loading inverter, (b) FO4 inverter, (c) 11-stage ring-oscillator.

related to the high and low logic state ( $NM_H$  and  $NM_L$ , respectively), are quite lower for the TFET inverter, as shown in Fig.4e. This issue is in part due to different  $T_P$  and  $T_N$  I-Vs, and in part to the combined effects of the superliner output-characteristics at very low  $V_{DS}$  (Fig.1b) and of the almost saturated transfer-characteristics at high current levels (Fig.1a), which lead to a wider transition for the TFET inverter VTC [14]. For this reason, although the  $NM_{H/L}$  can be balanced with an adequate sizing (e.g.  $W_P/W_N=3/1$ ), they still remain lower than the ones of the FinFET inverter with  $W_P/W_N=1/1$  (Fig.4e).

#### B. Performance optimization

The basic logic blocks of Fig.5 have been simulated with nominal TFETs in order to investigate the performance trends for different  $W_P/W_N$  conditions.

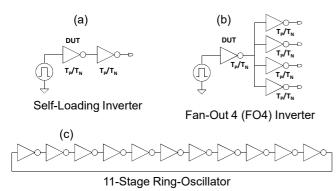

The TFET inverter either is loaded by an equal stage (selfloading inverter in Fig.5a) or by 4 equal stages (FO4 inverter in Fig.5b). For these configurations, rise and fall times are extracted and summarized in Fig.6 as a function of the WP/WN ratio, by assuming near to ideal input signals (i.e. negligible rise/fall times). The rise and fall times are defined as the delay from the 10% to the 90% of the transition of the output waveform. For both loading conditions, a W<sub>P</sub>/W<sub>N</sub> ratio larger than 1 allows to reduce the rise time (the minimum rise time correspond to a  $W_P/W_N$  of 2/1 and 3/1 for the self-loading and FO4 inverters, respectively). On the other hand, the average time monotonically increases with the increasing W<sub>P</sub>/W<sub>N</sub> ratio, due to the trends of the fall-transitions which are dominant. Clearly, such results depend on the input waveform, that is an ideal square waveform in this case, and thus the impact of the device input capacitance is not appropriately accounted for. In order to circumvent this issue, we have considered also the ring-oscillator (Fig.5c).

The critical path of a digital circuit sets a limit for the maximum frequency at which the circuit can operate. It usually depends on the device technology, the logic depth, the sizes of transistors, the load capacitance and the considered  $V_{DD}$ . The ring-oscillator is conventionally used for benchmarking purposes, because the ratio between the oscillation period  $(T_{osc})$  and the critical path delay of a generic circuit is, at a first

Fig. 6. 10% (90%) to 90% (10%) rise (fall) time for (a) Self-loading TFET inverter and (b) FO4 TFET inverter.  $V_{DD} = 400 \text{mV}$ .

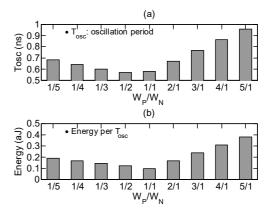

Fig. 7. TFET ring oscillator: (a) oscillation period (Tosc) and (b) energy per oscillation period vs. the  $W_P/W_N$  ratio of inverters.  $V_{DD} = 400mV$ .

order, independent from the technology, transistor sizing, temperature and  $V_{DD}$  [31]. For this reason, we have used a 11-stage ring oscillator to optimize the  $W_P/W_N$  ratio with respect to the  $T_{osc}$ , which is strongly correlated with the critical path delay of a generic circuit, and to the energy per  $T_{osc}$ , which in turn is correlated with the energy per operation when the same digital circuit is operated at the maximum frequency (for a particular  $V_{DD}$ ). In Fig.7a, the minimum  $T_{osc}$  corresponds to  $W_P/W_N=1/2$ , that is for symmetric  $T_P$  and  $T_N$  capacitances (and not for symmetric currents), whereas the minimum energy in Fig.7b corresponds to the minimum device area ( $W_P/W_N=1/1$ ), that is to the condition of minimum overall intrinsic capacitance.

In conclusion, although symmetric TFET drive-currents lead to improved noise margins, from the performance and energy consumption point of view, symmetric and as small as possible intrinsic capacitances are required.

# IV. FULL-ADDERS BENCHMARK

The conventional 28T full-adder [32,23] has been implemented exploiting TFET and FinFET solutions , and the two designs have been compared in terms of performance and energy figures-of-merit. The average energy per cycle as a function of  $V_{DD}$  for both TFET and FinFET 32-bit ripple carry adders (RCAs) is also considered, where for each  $V_{DD}$  the cycle is set to the minimum clock period limited by the critical path given by  $31 \cdot t_{Prop}+max\{t_{Prop},t_{Sum}\}$  [32], where  $t_{Prop}$  and  $t_{Sum}$  are the propagation delay (carry-in to carry-out delay) and the

(c) 2016 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other users, including reprinting/ republishing this material for advertising or promotional purposes, creating new collective works for resale or redistribution to servers or lists, or reuse of any copyrighted components of this work in other works. DOI: 10.1109/TED.2016.2566614 - © 2016 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

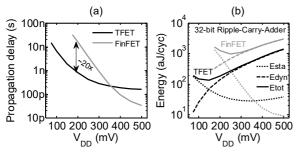

Fig. 8. (a) Propagation delay of 28T full-adders. (b) Energy per cycle as a function of  $V_{DD}$  for 32-bit ripple-carry-adders (implemented with 32 28T full-adders). The static and dynamic components are also shown separately. Nominal simulations performed on devices whose currents were aligned at  $I_{off} = 35 \text{ pA}$  (see [19]).

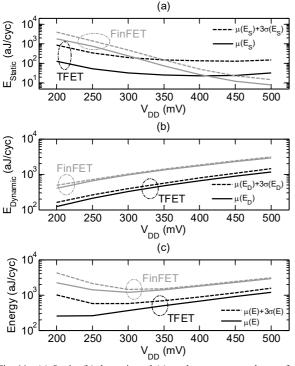

sum delay of the single-bit full-adder, respectively. Static and dynamic energy contributions are decoupled<sup>3</sup> in order to be investigated independently. At high  $V_{DD}$ , the dynamic energy (proportional to  $V_{DD}^{-2}$ ) is dominant. When  $V_{DD}$  decreases toward ultra-low voltage levels, despite the linear proportionality of the static power to  $V_{DD}$ , there is a severe increase of the static energy due to the longer critical path delay. As a result, the minimum energy per cycle corresponds to the  $V_{DD}$  value where the dynamic and static components are well balanced.

Thus, although performance is not the main factor on which we should base the comparison of technologies operated in the ultralow voltage regime, it is anyhow convenient to investigate the trends of the critical path delay with V<sub>DD</sub>, considering that it plays a fundamental role in the static energy consumption (proportional to the static power and to the duration of the cycle). For the sake of completeness, results obtained for nominal simulations [19] are also reported (Fig.8). The TFET full-adder becomes faster (i.e. lower propagation-delay) than the FinFET counterpart for V<sub>DD</sub> below ~350 mV (Fig.8a). In Fig.8b, the reduced performance degradation for the TFET circuit translates in a reduced increase of the static energy component for lower V<sub>DD</sub>s. This is the basic reason allowing the TFET circuit to reach a lower minimum energy point (135 aJ/cyc vs. 976 aJ/cyc) at a lower  $V_{DD}$  (150 mV vs. 250 mV). In fact, for nominal simulations, the 32-bit RCA implemented with TFETs is ~7.23x more energy efficient than the FinFET counterpart when both operate at the  $V_{DD}$  corresponding to the minimum energy point [19].

#### A. Evaluation of the minimum $V_{DD}$

As opposite to symmetric  $M_P$  and  $M_N$  FinFETs, the  $T_P$ - $T_N$  asymmetry may affect the correct operation of the TFET full-

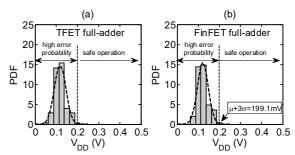

Fig. 9. Distributions of the minimum  $V_{DDS}$  allowing a successful sum operation (i.e. both S and Co bits are correct) under device VtV for (a) TFET and (b) FinFET 28T full-adders.

Fig. 10. Propagation delay (C to Co in propagation mode) of the TFET (black lines) and FinFET (grey lines) 28T full-adders as a function of  $V_{DD}$ . Solid lines: mean value; dashed lines: " $\mu$ +3 $\sigma$ " value.

adder at low V<sub>DD</sub>s when the VtV is considered. Thus, for each of the 8 possible input combinations (i.e. {A,B,C} = {0/1,0/1,0/1}), we have simulated 100 MC instances in order to evaluate the minimum V<sub>DD</sub>. These points have been used to obtain the probability density functions (PDFs) in Fig.9, where the " $\mu$ +3 $\sigma$ " values delineate the boundary between a region with a high error probability and a safe operating region. Interestingly, despite the W<sub>P</sub>/W<sub>N</sub> asymmetry at V<sub>DD</sub> = 400mV, the distributions of the minimum V<sub>DD</sub>s for TFET and FinFET full-adders are very similar (with practically the same " $\mu$ +3 $\sigma$ " boundary). For this reason, we have identified the W<sub>P</sub>/W<sub>N</sub>=1/1 condition as the most suitable for the rest of the analysis. This choice is also supported by argument that the lower energy condition is met for the 1/1 ratio, as shown in section III-B for the ring oscillator test circuit.

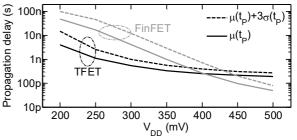

#### B. Performance and energy degradation with VtV

The same figures-of-merit in Fig.8 have been evaluated by including the VtV (with the I<sub>off</sub> realigned as shown in Fig.3), and then extracting both the mean ( $\mu$ ) values as well as the " $\mu$ +3 $\sigma$ " values for the related performance metric. From the propagation delay point of view, the variability is strongly related to the sensitivity of the on-current to the VtV, which is less variable for the TFET circuit for almost the entire range of investigation as evidenced by Fig.10: by comparing the " $\mu$ " with the " $\mu$ +3 $\sigma$ " lines, it is easy to relate the propagation delay variability with the normalized transconductance ( $g_m/I_{D,ON}$ ) at the corresponding V<sub>DD</sub>. In fact, conversely to FinFETs, which are always in the sub threshold region in the investigated voltage range, the almost saturated I<sub>D</sub>-V<sub>GS</sub> of TFETs at large V<sub>GS</sub> directly translates in a lower variability of the delay.

<sup>&</sup>lt;sup>3</sup> Transient simulations are performed for 100-bit long random A, B and C stimuli, with a constant bit-period ( $T_{bit} = 100$  ns, for an overall  $T_{sim}$  of 10µs). The average static power is estimated from the settled current sampled at the end of each  $T_{bit}$ . The average dynamic energy (Energy/cycle) is computed by integrating the product  $V_{DD}$ · $i_{DD}(t)$  over the simulation time (normalized to the single cycle) and by subtracting the static contribution. In plots reporting the Energy as a function of  $V_{DD}$ , the switching activity of the circuit (affecting the dynamic energy component) is given by the randomness of the stimuli, whereas the static component is weighted on the critical path delay.

(c) 2016 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other users, including reprinting/ republishing this material for advertising or promotional purposes, creating new collective works for resale or redistribution to servers or lists, or reuse of any copyrighted components of this work in other works. DOI: 10.1109/TED.2016.2566614 - © 2016 IEEE. Personal use is permitted. but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

Fig. 11. (a) Static, (b) dynamic and (c) total energy per cycle as a function of  $V_{DD}$  for TFET (black lines) and FinFET (grey lines) 32-bit ripple-carry-adders. Solid lines: mean value; dashed lines: " $\mu$ +3 $\sigma$ " value.

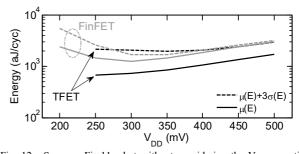

On the other hand, the TFET steep characteristics at low V<sub>GS</sub> becomes dramatic in terms of leakage variability, which affects the static component of the energy per cycle, as shown in Fig.11a. The variability of the dynamic energy components in Fig.11b of both TFET and FinFET implementations is practically negligible if compared to the ones of the static energy, since they are related just to the variability of device capacitance characteristics ( $E_{dyn} \propto C_{eq} V_{DD}^2$ ). Fig.11c shows the effect of VtV on the overall energy per cycle. Considering the average values, the TFET RCA has a minimum energy point of 263 aJ/cyc at 200 mV (note that the V<sub>DD</sub> cannot be further scaled down due to variability issues, as demonstrated by Fig.9), whereas the one of the FinFET implementation is 1194 aJ/cyc at 300 mV. This means that the energy improvement that is achieved with the TFET RCA is of ~4.54x with respect to the case with FinFETs (this factor is lower than the one estimated from nominal simulations [19]). When considering the " $\mu$ +3 $\sigma$ " trends, the energy saving with the TFET circuit further decreases, particularly due to the strong variability of the TFET static energy, that leads to a rightward shift of the minimum energy point (572 aJ/cyc at 300 mV), whereas the minimum energy point for the FinFET case is still at 300 mV (as for the "µ" case) but increases to 1440 aJ/cyc.

In summary, the VtV tends to lower the energy improvements of TFET circuits when compared to their FinFET counterparts. This basically means that research efforts for steeper and steeper devices should be accompanied by improvements of the reproducibility of fabricated device characteristics, considering that the VtV becomes an increasing issue with the increasing  $g_m/I_D$  (i.e. with the

Fig. 12. Same as Fig.11c, but without considering the  $V_{\rm off}$  correction in Fig.3.

decreasing SS) at current levels close to the Ioff target.

It is worth nothing that these results have been achieved with the devices transfer-characteristics aligned at the same  $\mu(I_{off})$ , performed at the beginning of this study to partially counteract the different sensitivity of the TFET and FinFET leakage with respect to the VtV. Fig.12 shows the same plot of the energy per cycle versus  $V_{DD}$  as in Fig.11c, but considering the device transfer-characteristics aligned at the same  $I_{off}$  for nominal TFET and FinFET devices, but different  $\mu(I_{off})$  when the VtV is considered. In this case, the TFET advantages in terms of energy are almost completely lost due to the larger impact of the leakage variability for TFET devices.

#### V. CONCLUSION

In this study, we have compared two virtual complementary platforms (namely, the T<sub>P</sub> and T<sub>N</sub> heterojunction III-V TFETs and the M<sub>P</sub> and M<sub>N</sub> FinFETs) in the ultra-low voltage regime, with emphasis on the implications of the device V<sub>th</sub> variability on the dynamic and static characteristics of digital circuits. Unlike the M<sub>P</sub> and M<sub>N</sub> FinFETs, the T<sub>P</sub> and T<sub>N</sub> TFETs feature an asymmetry in the drive-current. This limit can be partially addressed by a careful sizing of the W<sub>P</sub>/W<sub>N</sub> ratio, at least from the noise margins point of view. Neverthless, from the speed and energy point of view, effects as the unbalancing of the T<sub>P</sub>-T<sub>N</sub> intrinsinc capacitances and the increase of the overall effective capacitance, tend to be more detrimental than the improvements which are obtained thanks to the balanced drive-currents. The 32 bit ripple carry adders designed using 28T full-adder blocks, have been used to benchmark the TFET and FinFET tecnologies, by considering the same condition of variability for the Vth. Due to different slope of the turn-on characteristics, it is recommended to preventively consider the Vth variability, by aligning the device ID-VGSs so as to ensure a iso-leakage condition when the VtV is considered (same average value of the I<sub>off</sub>). This guideline allows to keep the static energy below the dynamic energy component at higher V<sub>DD</sub>, so as that the TFET implementation can reach a lower minimum energy point (as for nominal simulations). Even so, by assuming the same V<sub>th</sub> variability, the energy improvement which can be obtained with TFETs tends to be lower than the one estimated from nominal simulations. This means that a steep device intrinsically needs a superior control of process variation items in order to completely exploit the possible advantages related to the low SS.

(c) 2016 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other users, including reprinting/ republishing this material for advertising or promotional purposes, creating new collective works for resale or redistribution to servers or lists, or reuse of any copyrighted components of this work in other works. DOI: 10.1109/TED.2016.2566614 - © 2016 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

#### References

- Baravelli, E.; Gnani, E.; Grassi, R.; Gnudi, A.; Reggiani, S.; Baccarani, G., "Optimization of n- and p-type TFETs Integrated on the Same InAs/AlxGa1-xSb Technology Platform", *IEEE Transactions on Electron Devices*, vol.61, no.1, pp.178-185, Jan. 2014. DOI: 10.1109/TED.2013.2289739.

- [2] Baravelli, E.; Gnani, E.; Gnudi, A.; Reggiani, S.; Baccarani, G., "TFET Inverters With n-/p-Devices on the Same Technology Platform for Low-Voltage/Low-Power Applications", *IEEE Transactions on Electron Devices*, vol.61, no.2, pp.473-478, Feb. 2014. DOI: 10.1109/TED.2013.2294792.

- [3] Luisier, M.; Klimeck, G., "Performance comparisons of tunneling fieldeffect transistors made of InSb, Carbon, and GaSb-InAs broken gap heterostructures", 2009 IEEE International Electron Devices Meeting (IEDM), pp.1-4, 7-9 Dec. 2009. DOI: 10.1109/IEDM.2009.5424280.

- [4] A. Sharma, A. A. Goud and K. Roy, "GaSb-InAs n-TFET With Doped Source Underlap Exhibiting Low Subthreshold Swing at Sub-10-nm Gate-Lengths", *IEEE Electron Device Letters*, vol. 35, no. 12, pp. 1221-1223, Dec. 2014. DOI: 10.1109/LED.2014.2365413.

- [5] M. G. Pala and S. Brocard, "Exploiting Hetero-Junctions to Improve the Performance of III-V Nanowire Tunnel-FETs", *IEEE Journal of the Electron Devices Society*, vol. 3, no. 3, pp. 115-121, May 2015. DOI: 10.1109/JEDS.2015.2395719.

- [6] Dewey, G.; Chu-Kung, B.; Boardman, J.; Fastenau, J.M.; Kavalieros, J.; Kotlyar, R.; Liu, W.K.; Lubyshev, D.; Metz, M.; Mukherjee, N.; Oakey, P.; Pillarisetty, R.; Radosavljevic, M.; Then, H.W.; Chau, R., "Fabrication, characterization, and physics of III–V heterojunction tunneling Field Effect Transistors (H-TFET) for steep sub-threshold swing", 2011 IEEE International Electron Devices Meeting (IEDM), pp.33.6.1-33.6.4, 5-7 Dec. 2011. DOI: 10.1109/IEDM.2011.6131666.

- [7] D. K. Mohata et al., "Demonstration of MOSFET-like on-current performance in arsenide/antimonide tunnel FETs with staggered heterojunctions for 300mV logic applications", 2011 IEEE International Electron Devices Meeting (IEDM), Washington, DC, pp. 33.5.1-33.5.4, 2011. DOI: 10.1109/IEDM.2011.6131665.

- [8] Guangle Zhou; Li, R.; Vasen, T.; Qi, M.; Chae, S.; Lu, Y.; Zhang, Q.; Zhu, H.; Kuo, J.-M.; Kosel, T.; Wistey, M.; Fay, P.; Seabaugh, A.; Huili Xing, "Novel gate-recessed vertical InAs/GaSb TFETs with record high ION of 180 μA/μm at VDS = 0.5 V", 2012 IEEE International Electron Devices Meeting (IEDM), pp.32.6.1-32.6.4, 10-13 Dec. 2012. DOI: 10.1109/IEDM.2012.6479154.

- [9] M. G. Pala and D. Esseni, "Interface Traps in InAs Nanowire Tunnel-FETs and MOSFETs—Part I: Model Description and Single Trap Analysis in Tunnel-FETs", *IEEE Transactions on Electron Devices*, vol. 60, no. 9, pp. 2795-2801, Sept. 2013. DOI: 10.1109/TED.2013.2274196.

- [10] S. Datta, R. Bijesh, H. Liu, D. Mohata and V. Narayanan, "Tunnel transistors for energy efficient computing", 2013 IEEE International Reliability Physics Symposium (IRPS), pp. 6A.3.1-6A.3.7, Anaheim, CA, 2013. DOI: 10.1109/IRPS.2013.6532046.

- [11] E. Lind, E. Memišević, A. W. Dey and L. E. Wernersson, "III-V Heterostructure Nanowire Tunnel FETs", *IEEE Journal of the Electron Devices Society*, vol. 3, no. 3, pp. 96-102, May 2015. DOI: 10.1109/JEDS.2015.2388811.

- [12] Sinha, S.; Yeric, G.; Chandra, V.; Cline, B.; Yu Cao, "Exploring sub-20nm FinFET design with Predictive Technology Models", 2012 49th ACM/EDAC/IEEE Design Automation Conference (DAC), pp.283-288, 3-7 June 2012. DOI: 10.1145/2228360.2228414.

- [13] URL: http://ptm.asu.edu.

- [14] Y. N. Chen, M. L. Fan, V. P. H. Hu, P. Su and C. T. Chuang, "Design and Analysis of Robust Tunneling FET SRAM", *IEEE Transactions on Electron Devices*, vol. 60, no. 3, pp. 1092-1098, March 2013. DOI: 10.1109/TED.2013.2239297.

- [15] D. H. Morris, U. E. Avci, R. Rios, I. A. Young, "Design of Low Voltage Tunneling-FET Logic Circuits Considering Asymmetric Conduction Characteristics", *IEEE Journal on Emerging and Selected Topics in Circuits and Systems*, vol. 4, no. 4, pp. 380-388, Dec. 2014. DOI: 10.1109/JETCAS.2014.2361054.

- [16] U. E. Avci, D. H. Morris, I. A. Young, "Tunnel Field-Effect Transistors: Prospects and Challenges", *IEEE Journal of the Electron Devices Society*, vol. 3, no. 3, pp. 88-95, May 2015. DOI: 10.1109/JEDS.2015.2390591.

- [17] Strangio, S.; Palestri, P.; Esseni, D.; Selmi, L.; Crupi, F.; Richter, S.; Qing-Tai Zhao; Mantl, S., "Impact of TFET Unidirectionality and Ambipolarity on the Performance of 6T SRAM Cells", *IEEE Journal of the Electron Devices Society*, vol.3, no.3, pp.223-232, May 2015. DOI: 10.1109/JEDS.2015.2392793.

- [18] Lanuzza, M.; Strangio, S.; Crupi, F.; Palestri, P.; Esseni, D., "Mixed Tunnel-FET/MOSFET Level Shifters: A New Proposal to Extend the Tunnel-FET Application Domain", IEEE *Transactions on Electron Devices*, vol.62, no.12, pp.3973-3979, Dec. 2015. DOI: 10.1109/TED.2015.2494845.

- [19] S. Strangio, P. Palestri, M. Lanuzza, D. Esseni, F. Crupi and L. Selmi, "Benchmarks of a III-V TFET Technology Platform against the 10-nm CMOS Technology Node Considering 28T Full-Adders", 2016 Joint International EUROSOI Workshop and International Conference on Ultimate Integration on Silicon (EUROSOI-ULIS), Vienna, Jan. 2016. (ISBN 978-1-4673-8609-8, pp. 139-142).

- [20] TCAD Sentaurus Device U.G., version G-2012.06, 2012.

- [21] URL: http://www.ioffe.ru/SVA/NSM/Semicond/.

- [22] M. J. M. Pelgrom, A. C. J. Duinmaijer and A. P. G. Welbers, "Matching properties of MOS transistors", *IEEE Journal of Solid-State Circuits*, vol. 24, no. 5, pp. 1433-1439, Oct 1989. DOI: 10.1109/JSSC.1989.572629.

- [23] F. Conzatti, M. G. Pala and D. Esseni, "Surface-Roughness-Induced Variability in Nanowire InAs Tunnel FETs", *IEEE Electron Device Letters*, vol. 33, no. 6, pp. 806-808, June 2012. DOI: 10.1109/LED.2012.2192091.

- [24] K. M. Choi and W. Y. Choi, "Work-Function Variation Effects of Tunneling Field-Effect Transistors (TFETs)", *IEEE Electron Device Letter*, vol. 34, no. 8, pp. 942-944, 2013. DOI: 10.1109/LED.2013.2264824.

- [25] A. Sharma, A. A. Goud and K. Roy, "GaSb-InAs n-TFET With Doped Source Underlap Exhibiting Low Subthreshold Swing at Sub-10-nm Gate-Lengths", *IEEE Electron Device Letters*, vol. 35, no. 12, pp. 1221-1223, Dec. 2014. DOI: 10.1109/LED.2014.2365413.

- [26] D. Esseni, M.Guglielmini, B. Kapidani, T. Rollo, M. Alioto, "Tunnel FETs for Ultralow Voltage Digital VLSI Circuits: Part I—Device– Circuit Interaction and Evaluation at Device Level", *IEEE Transactions* on Very Large Scale Integration (VLSI) Systems, vol. 22, no. 12, pp. 2488-2498, Dec. 2014. DOI: 10.1109/TVLSI.2013.2293135.

- [27] N. Agrawal, H. Liu, R. Arghavani, V. Narayanan and S. Datta, "Impact of Variation in Nanoscale Silicon and Non-Silicon FinFETs and Tunnel FETs on Device and SRAM Performance", *IEEE Transactions on Electron Devices*, vol. 62, no. 6, pp. 1691-1697, June 2015. DOI: 10.1109/TED.2015.2406333.

- [28] D. H. Morris, U. E. Avci and I. A. Young, "Variation-tolerant dense TFET memory with low VMIN matching low-voltage TFET logic", 2015 Symposium on VLSI Technology (VLSI Technology), pp. T24-T25, Kyoto, 2015. DOI: 10.1109/VLSIT.2015.7223688.

- [29] Y.X. Liu, K. Endo, S. O'uchi, T. Kamei, J. Tsukada, H. Yamauchi, Y. Ishikawa, T. Hayashida, K. Sakamoto, T. Matsukawa, A. Ogura, M. Masahara, "On the gate-stack origin threshold voltage variability in scaled FinFETs and multi-FinFETs", *Symposium on VLSI Technology (VLSIT)* 2010, pp. 101-102, 15-17 June 2010. DOI: 10.1109/VLSIT.2010.5556187.

- [30] A. Paul et al., "Comprehensive study of effective current variability and MOSFET parameter correlations in 14nm multi-fin SOI FINFETS", 2013 IEEE International Electron Devices Meeting (IEDM), Washington, DC, pp. 13.5.1-13.5.4, 2013. DOI: 10.1109/IEDM.2013.6724625.

- [31] Macken, P.; Degrauwe, M.; Van Paemel, M.; Oguey, H., "A voltage reduction technique for digital systems", *37th IEEE International Solid-State Circuits Conference (ISSCC)*, pp.238-239, 14-16 Feb. 1990. DOI: 10.1109/ISSCC.1990.110213.

- [32] Neil Weste and David Harris. 2010. CMOS VLSI Design: A Circuits and Systems Perspective (4th ed.). Addison-Wesley Publishing Company, USA.

- [33] Alioto, M.; Palumbo, G., "Analysis and comparison on full adder block in submicron technology", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol.10, no.6, pp.806-823, Dec. 2002. DOI: 10.1109/TVLSI.2002.808446.