# The integrated low-level trigger and readout system of the CERN NA62 experiment

R. Ammendola<sup>a</sup>, B. Angelucci<sup>b,3</sup>, M. Barbanera<sup>c</sup>, A. Biagioni<sup>d</sup>, V. Cerny<sup>e</sup>, B. Checcucci<sup>f</sup>, R. Fantechi<sup>c</sup>, F. Gonnella<sup>g,2</sup>, M. Koval<sup>e,4</sup>, M. Krivda<sup>h</sup>, G. Lamanna<sup>i</sup>, M. Lupi<sup>j,4</sup>, A. Lonardo<sup>d</sup>, A. Papi<sup>f</sup>, C. Parkinson<sup>h,2</sup>, E. Pedreschi<sup>i</sup>, P. Petrov<sup>k</sup>, R. Piandani<sup>c</sup>, J. Pinzino<sup>i,4</sup>, L. Pontisso<sup>c,5</sup>, M. Raggi<sup>g</sup>, D. Soldi<sup>l</sup>, M. S. Sozzi<sup>i,\*</sup>, F. Spinella<sup>c</sup>, S. Venditti<sup>b,3</sup>, P. Vicini<sup>d</sup>

a INFN, Section of Roma Tor Vergata, Via d. Ricerca Scientifica 1, 00133 Roma IT

b Department of Physics, University of Pisa, Largo B. Pontecorvo 3, 56127 Pisa IT

c INFN, Section of Pisa, Largo B. Pontecorvo 3, 56127 Pisa IT

d INFN, Section of Roma, Piazzale A. Moro 2, 00185 Roma IT

e Faculty of Mathematics, Physics and Informatics, Comenius University, Mlynska dolina, 84248 Bratislava, SK

f INFN, Section of Perugia, Via A. Pascoli 23C, 06123 Perugia IT

s INFN, Laboratori Nazionali di Frascati, Via E. Fermi 40, 00044 Frascati IT

h School of Physics and Astronomy, University of Birmingham, Edgbaston Birmingham B15 2TT UK

i Department of Physics, University of Pisa and INFN, Section of Pisa, Largo B. Pontecorvo 3, 56127 Pisa IT

j Department of Engineering, University of Perugia and INFN, Section of Perugia, Via A. Pascoli 23C, 06123 Perugia IT

k Université Catholique de Louvain, B-1348 Louvain-La-Neuve, BE

i Department of Physics, University of Torino and INFN, Section of Torino, Via P. Giuria 1, 10125 Torino IT

#### **Abstract**

The integrated low-level trigger and data acquisition (TDAQ) system of the NA62 experiment at CERN is described. The requirements of a large and fast data reduction in a high-rate environment for a medium-scale, distributed ensemble of many different sub-detectors led to the concept of a fully digital integrated system with good scaling capabilities. The NA62 TDAQ system is rather unique in allowing full flexibility on this scale, allowing in principle any information available from the detector to be used for triggering. The design concept, implementation and performances from the first years of running are illustrated.

Keywords: Trigger, Data Acquisition, High-Energy Physics, Digital electronics

PACS: 07.05.Hd, PACS: 07.50.Ek PACS: 07.05.Bx PACS: 07.05.Wr

## 1. Introduction

The main goal of the NA62 experiment at CERN [1] is the measurement of the branching ratio (BR) of the ultra-rare kaon decay mode  $K^+ \to \pi^+ \nu \bar{\nu}$ : such quantity is predicted in the Standard Model (SM) with a

high precision [2], quite unusual for hadronic decays, and therefore represents a very powerful probe of possible New Physics. Moreover, in case a discrepancy with the SM prediction is measured, the "theoretically clean" predictions of such flavour-changing neutral current decay BR would also allow to discriminate among different classes of SM extensions. The downside is that the expected branching ratio is exceedingly small, of order  $10^{-10}$ , and the only existing measurement [3] is based on 7 candidate events, thus lacking any real discriminating power due to its limited precision. The NA62 experiment, which aims to make a 10% measurement of the  $K^+ \to \pi^+ \nu \bar{\nu}$  BR using a novel high-energy decay-inflight approach, just concluded its first data taking pe-

<sup>\*</sup>Corresponding author

<sup>&</sup>lt;sup>1</sup>Now at School of Physics and Astronomy, University of Birmingham, Edgbaston Birmingham B15 2TT UK.

<sup>&</sup>lt;sup>2</sup>Supported by ERC Starting Grant 336581.

<sup>&</sup>lt;sup>3</sup>Now at CAEN S.p.A., Via della Vetraia, 11, 55049 Viareggio LU.

<sup>&</sup>lt;sup>4</sup>Now at CERN, CH-1211 Geneva 23, CH.

$<sup>^5\</sup>mbox{Now}$  at INFN, Section of Roma, Piazzale A. Moro 2, 00185 Roma IT.

riod.

To achieve the required precision, NA62 must collect  $O(10^{13})$  kaon decays, accompanied by a rejection factor of  $O(10^{12})$  to suppress the huge background from other kaon decays. Part of this suppression must already be made at the trigger level, in order to reduce the amount of data that needs to be stored and analysed. Such a large event sample also provides an opportunity to perform many other studies of kaon decays, which can result in significant improvements on searches for symmetry violations and in the understanding of QCD and its low-energy effective approximation, which are indeed secondary goals of the NA62 experiment. Thus the trigger system must be flexible as well as highly selective.

The NA62 detector is currently composed of 16 subdetectors spatially distributed along more than 200 m of beam line, before, around and after a 65 m long decay region [1]. Kaons are delivered to the experiment via a high-intensity 75 GeV/c hadron beam, with a beam particle rate close to 1 GHz. The decays of beam particles ( $\sim$  6% being  $K^+$ ) result in an event rate in excess of 10 MHz in the sub-detectors situated after the decay region. Excellent time resolution at the trigger level is therefore mandatory, while the minimisation of data collection dead-time, and the maximisation of efficiency and reliability, also rank high in importance. These considerations led to the adoption of a multi-level trigger system.

The lower trigger level, denoted as Level 0 (L0)<sup>6</sup> is implemented in hardware and works on data from faster sub-detectors at the full event rate, of order 10 MHz, reducing it by a factor 10 and driving the readout of data at 1 MHz to an on-line farm of commercial processors (PC farm), on which further High Level Trigger (HLT) selections are performed in software. The HLT includes a first level (L1) working on single sub-detector information, reducing the rate to 100 kHz and triggering the completion of the readout for the remaining data-heavy sub-detectors (the beam spectrometer and the calorimeters), and a second level (L2) working on the full detector information.

This article describes the design and implementation of the L0 trigger level of NA62, which has the distinctive characteristic of being fully integrated with the readout system for most sub-detectors.

#### 2. Overall design

The L0 trigger system is fully digital, and is designed to work on the main data stream of the experiment: this unification of the (usually distinct) data and trigger paths presents several advantages, among which are the reduction of the amount of hardware, and the complete control and monitoring of the trigger performance, reproducible at bit level on collected control data. Most importantly, the above approach imposes no limitations in principle on the kind of trigger processing which can be performed. This is an important asset in an experiment using a novel approach, in which trigger conditions are expected to evolve both because of the experience gained during data-taking, and the possibility of expanding the physics programme.

The reason why such approach was not normally implemented by earlier experiments, which usually rely on separated hardware (often partly analogue) trigger systems handling a reduced sub-set of detector information, is related to the amount of data which needs to be read-out autonomously before a trigger is issued and temporarily stored while the trigger decision is being evaluated. Current technology, and in particular the decreasing cost of digital memories, allows a high-rate experiment with a total channel count of order 100 thousand such as NA62 to fully store its digitized data for a quite long time compared to the average inverse event rate.

Besides the main concept of full integration of the L0 trigger and data acquisition systems, two more key points in the design were the use of a single unified path for trigger and control of individual system boards, and the use of common Gigabit Ethernet (GbE) output data links. The first point follows an established trend in HEP experiments, and allowed the use of existing hardware developed for LHC experiments. The second one, besides its advantages in terms of cost and simplicity, resulted in a large flexibility and scalability in the PC farm through a switched network. This flexibility was exploited to adapt to different running conditions, for example: by changing the bandwidth sharing between L0 trigger information and main read out data; and by changing to higher-performance processors in the PC farm without needing to change the L0 system.

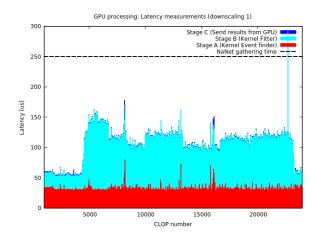

As mentioned, the L0 trigger system works on the full event rate, in excess of 10 MHz, and its rejection factor of about 10 is expected to match the design maximum readout rate of 1 MHz for most sub-detectors. The latency of the L0 trigger system was chosen to be 1 ms, a rather large value compared to usual implementations, to possibly allow the use of massively-parallel proces-

<sup>&</sup>lt;sup>6</sup>Distinctively reserving positive numbers for software trigger levels.

sors already at this level, as the recent dramatic increase in performance for such devices suggested (see section 10).

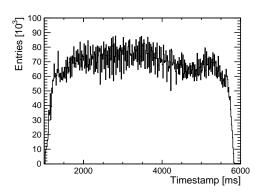

In the following we describe the overall scheme of the common integrated readout and L0 trigger system used for most detectors in NA62, whose elements are detailed in individual sections, starting with information on the backbone structure which allows the entire system to work in a tightly-synchronized way (section 3). As a fixed-target experiment running at the CERN SPS accelerator, NA62 receives beam in a periodic way, with bursts of a few seconds duration every several tens of seconds (up to about one minute). The time structure of bursts is (roughly) constant during each data-taking run of a few-hours duration, but can change significantly on a daily level, depending on the accelerator working mode. Bursts naturally define coherent data-taking units, down to the level of a final data file for permanent storage, identified by a unique burst identifier. This was chosen to be the UNIX time of a conveniently chosen instant of the burst itself, encoded as a signed 32-bit number and centrally assigned by the PC farm management system and broadcast over the network. Sub-systems' synchronization is achieved through the use of the common timestamp, defined as a 32-bit unsigned word with 25 ns least significant bit. The timestamp is locally generated in each individual electronic board from the common distributed 40 MHz clock, and fully synchronized throughout the entire system at the start of every burst.

Events are processed by custom electronics and stored into temporary buffers for 1 ms, waiting for a L0 trigger decision; in the common system this is done on the TEL62 boards (section 4) and their daughter-cards (section 5). During such latency, the L0 trigger is elaborated on the full information from participating subdetectors, producing data (L0 trigger primitives) indicating the fulfilment of several programmable criteria at the same rate (sections 6, 7) at which events occur. Such processing is performed in a time-asynchronous way, thus allowing to exploit the same cheap packet-based network protocol used for data readout.

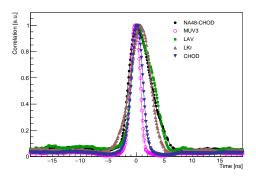

The sub-detectors participating to the L0 trigger decision are currently: two plastic scintillator hodoscopes (NA48-CHOD, with a bar layout, and CHOD with a pad layout) and a Ring-Imaging Čerenkov detector (RICH), both mainly used for timing and trackidentification; coarse-grained digital data<sup>7</sup> from cells

of the electro-magnetic (LKr) and hadronic (MUV1, MUV2) calorimeters; lead-glass ring-shaped detectors surrounding the decay region (LAV) and small auxiliary detectors (SAC, IRC) for vetoing photons; and a plane of plastic scintillator pads behind an iron wall (MUV3) for vetoing muons. Data from the above detectors provide the required factor 10 rate reduction. L0 trigger primitives are partially time-ordered, grouped into Multi-Trigger Packets (MTPs) and sent through one GbE link per sub-detector to the central L0 Trigger Processor (L0TP). These primitives are also read-out independently for monitoring purposes (section 8).

The L0TP (section 9) time-matches and processes the above primitives to concurrently check several programmable L0 trigger conditions. Inclusion of more sub-detectors is possible, to further refine the trigger conditions or to collect alternative data samples. L0 trigger primitive generation is required to occur within a programmable, fixed time limit (up to several hundreds of  $\mu$ s) after the event time, in order to allow the L0TP to make its decision based on all the available information. To ease the time matching task of the L0TP, MTPs are expected to be delivered roughly (because of variable network latencies) every 6.4  $\mu$ s.

The L0TP issues a L0 trigger decision which eventually drives the data transfer to the PC farm. Actually, the two most data-heavy sub-detectors only save event data onto secondary (longer-latency) internal buffers, and send it to the PC farm only in case of a subsequent positive L1 trigger signal.

The L0 trigger decision is issued in a synchronous way<sup>8</sup>, thus allowing a simplification of the trigger distribution network, which shares links with the clock and timing distribution network. Each L0 trigger carries a timestamp with 25 ns granularity, identifying which data should be transferred to the PC farm, in time windows whose size can depend on the individual sub-detector; a trigger-type qualifier is also dispatched, which allows both a different data handling for different trigger classes (including e.g. calibration and monitoring triggers), as well as the use of the very same L0 trigger path for broadcasting commands related to the functioning, synchronization, integrity and flow control of the entire TDAQ framework, with a further unification of links. The timestamp associated to each L0-triggered event is defined by the LOTP, and for each burst it is in unique relationship with a sequential event number. The consistency between timestamp and event number

<sup>&</sup>lt;sup>7</sup>Coarse-graining is required because of the sheer amount of electro-magnetic calorimeter data, from 13 thousand 40 MHz continuously digitized channels, which cannot be made fully available within the time constraints of L0, see section 7.

<sup>&</sup>lt;sup>8</sup>In this context "synchronous" denotes a signal occurring in a precisely defined 25 ns time-slot with respect to its originating cause, in this case the physics event in the detector.

is checked for all data (the timestamp being part of the event structure at all levels of data transport), as any mismatch would indicate an unacceptable trigger loss in part of the system, thus leading to data rejection.

Since vetoing efficiency and avoidance of undetected readout failures is crucial for the experiment, all subdetectors must provide a response to each L0 trigger, even if there is no data to be transferred. Furthermore, such responses always contain identifiable data structures originating in each individual readout board. The above implementation intrinsically provides the required control on the "live state" of all sub-detectors in each event. Another potentially dangerous misbehaviour of the TDAQ system would be a time mis-alignment between data from different subdetectors, resulting in data containing information belonging to different triggers. This is avoided by periodic time-alignment checks and event-by-event timestampmatching checks: all digital systems run on the same synchronous 40 MHz clock, thus allowing locally- and centrally-generated timestamps to be compared. Furthermore, each individual electronic board records the number of 25 ns clock periods counted during each burst, and such numbers are compared in order to identify any loss of time synchronization.

The unified data-path approach was pursued by extending it to the collection of "slow-control" monitoring information from the entire TDAQ system: at times (most notably at the end of each burst) special L0 triggers are dispatched, to which all boards react by sending monitoring data "events" along the standard data links. This approach does not require additional slow-control data paths, and ensures the availability of monitoring data together with the main data without needing additional book-keeping or data handling.

An extension of the system based on the hard realtime use of GPUs is described in section 10. Section 11 illustrates some results from the experience gained in running the system during the first data-taking period of the experiment, and some conclusions are presented in section 12.

# 3. Common infrastructure

## 3.1. Clock and L0 trigger distribution

A common master clock signal with a ~40 MHz frequency is generated by a single free-running high-stability oscillator<sup>9</sup> and optically distributed to all systems through modules of the Timing, Trigger and Con-

trol (TTC) system, designed at CERN for LHC experiments [4]. The master clock drives the entire TDAQ system and is used as the reference for all time measurements in NA62. While the common experiment timestamp is defined by such phase-coherent distributed clock, each sub-system locally generates by multiplication a properly locked reference for fine-time.

The master clock frequency is actually 40.078 MHz, since it must fall within the locking range of the QPLL (Quartz crystal Phase-Locked Loop) jitter-cleaning system [5] of the TTC system, used to guarantee the required clock accuracy and stability (such range was defined by the timing structure of the LHC machine). As a consequence all references to *e.g.* "25 ns" should be understood to be the period of the main clock, close to 24.951 ns, and similarly the "100 ps" fine-time unit is actually 97.466 ps<sup>10</sup>.

The master clock signal is distributed to a fan-out card, which drives in parallel 12 identical clock/trigger sub-systems. Each clock/trigger sub-system, normally serving a single sub-detector, comprises a modified version of the Local Trigger Unit (LTU) module [6] designed for the ALICE experiment, and a TTC laser encoder and transmitter module (TTCex) [7] with up to 10 identical optical outputs. Passive optical splitters provide up to 320 output links per sub-system, to individually feed all boards. Each electronics board requiring reference to the common experiment time is equipped with a TTC receiver (TTCrx) [8] chip decoding information from the optical signal, and optionally a QPLL system to reduce clock jitter.

All clock counters are simultaneously reset at the start of each burst, using a synchronous Start Of Burst signal (SOB) sent to all sub-systems through the TTC link before the arrival of the beam<sup>11</sup>. This signal also defines the origin of the time measurements for the current burst. An analogous synchronous End Of Burst (EOB) signal is sent in the same way about 1 s after the end of the burst, defining the largest possible timestamp, whose value is recorded by each system and sent to the PC farm for logging together with the data. This allows (on-line and off-line) consistency checks on the number of clock cycles counted by each system during each burst. Note that by resetting all local timestamp counters on SOB through the same link which delivers the clock, any relative delay between sub-systems

<sup>&</sup>lt;sup>9</sup>Hewlett Packard 8656B Signal Generator.

<sup>&</sup>lt;sup>10</sup>The exact frequency of the master clock is irrelevant for NA62, as long as it is constant throughout the system.

<sup>&</sup>lt;sup>11</sup>This is generated by time aligning "to 25 ns precision" the SPS Warning of Warning of Extraction (WWE) signal, which is issued roughly 1 second before the first beam particles are delivered.

due to propagation time differences is irrelevant. Each sub-detector readout system is capable of running in a standalone mode, autonomously generating its own TTC signals (possibly including L0 triggers) for test purposes, while during data-taking it runs under global experiment control.

When a L0 trigger is generated by the L0TP, a single optical link per board is used, via TTC time-multiplexing, to broadcast it to the rest of the experiment. The broadcast happens via two consecutive signals: the first is a "L0 trigger" pulse, the time of which defines the L0 trigger time to 25 ns precision; the second encodes a 6-bit "L0 trigger type", which is asynchronous with respect to the L0 trigger pulse. The TTC system imposes a 75 ns minimum time separation between two different L0 triggers, which is not an issue in principle, as the time occupancy of sub-detectors, and thus the chosen time widths of the readout windows, are larger than such figure.

The LTU provides the interface between the L0TP and the sub-detectors. The LTU receives signals from the L0TP, encodes and serializes them, and sends the data to the sub-detectors through the TTC system. It can also run in a stand-alone mode, in which it can emulate the generation of L0TP triggers, allowing each sub-detector to work independently during a debugging or calibration phase. The LTU also processes CHOKE/ERROR flow-control signals (section 3.2) from sub-detectors, and propagates them to the L0TP, where they are processed. The LTU also distributes SOB and EOB signals to all sub-detectors via the TTC system<sup>12</sup>.

The LTU provides the possibility to measure the phase of an incoming signal via an integrating RC circuit and an analog-to-digital converter, meaning appropriate delays for input signals can be applied to ensure proper time-alignment and latching.

## 3.2. Flow and error control

Two system-wide communication lines, named CHOKE and ERROR, are used by the TDAQ boards to provide feedback to the L0 trigger system concerning the occurrence of anomalous conditions which can impact the data-taking. Each board actively drives one CHOKE line and one ERROR line. All the CHOKE (ERROR) lines from the boards of a given sub-detector are OR-ed together by dedicated active fan-in boards

(CHEF), until there is a single pair of lines from the sub-detector. The pair of lines is then connected to the LOTP (section 9), via the sub-detector LTU, using point-to-point LVDS signals.

The CHOKE signal is used to indicate that (part of) a sub-system is approaching a state in which it will no longer be able to correctly handle data, because e.g. its processing or storage resources are almost saturated. If the asserted CHOKE from a sub-detector is not masked in the LOTP the dispatching of L0 triggers is stopped until all sub-detectors stop asserting the signal. The CHOKE signal is used to exert back-pressure from TDAQ boards in case of anomalous rate conditions, but its assertion is not associated to any critical malfunctioning or data loss. The ERROR signal is used instead to indicate that (part of) a sub-system actually lost some data because its processing capabilities were exceeded. Tight data integrity control is obtained by dispatching special L0 triggers whenever either the CHOKE or the ERROR condition is asserted or de-asserted (see section 9), and the mandatory replies to such triggers act as active acknowledgements by sub-systems, traceable in the data, that the above conditions were properly handled while such systems were fully working.

#### 3.3. Configuration

The state of the whole TDAQ system is centrally managed by the Experiment Control System (ECS), which runs a finite state machine. Two stages are foreseen to configure the TDAQ system: at the initialization stage a complete restart of the system is performed, uploading to the hardware all the configuration data which is not meant to change frequently, and which might require a relatively long set-up time (several minutes); at the start run stage a faster warm start occurs, in which further run-specific configuration data is uploaded. ECS communication is handled through the DIM system [9]. All configuration data is contained in human-readable XML files which are extracted from a database by a Run Control system, and stored into a condition database for each run. Most sub-systems also deliver some configuration data, together with monitoring information, within their End-Of-Burst data packet, making it readily available inside the event data files.

## 4. Common TDAQ board

The guiding principles driving the design of the TDAQ system were large channel integration, scalability and versatility, in order to optimize the implementation and maintenance effort, allowing use in a

<sup>&</sup>lt;sup>12</sup>These signals are encoded into the two lowest bits of the asynchronous TTC message byte, also containing the L0 trigger type. Such bits have defined reset behaviour for the TTC signal receivers, and are received at the same time by all boards within the TDAQ system.

large set of heterogeneous sub-detectors, while ensuring the possibility of significant changes in trigger configuration. A high-performance, general-purpose, versatile trigger and data-acquisition board, denoted TEL62 [11], was designed to be used by most sub-detectors in NA62, with enough flexibility to be suited for rather different daughter-cards (such as the TDCB time digitizer card, section 5). Most sub-detectors in NA62 use this common system for readout and (some of them) for L0 trigger primitive generation: the Čerenkov kaon tagger (KTAG), the charged particle scintillating veto counter (CHANTI), the downstream plastic scintillator hodoscopes (CHOD and NA48-CHOD), the main Čerenkov detector (RICH), the muon (MUV0, MUV3) and hadron (HASC) veto counters, the photon veto counters (LAV, SAC, IRC13). Some sub-detectors adopted instead other dedicated systems, either because of high-density sensor integration requirements for the silicon pixel GigaTracker beam spectrometer, or the preference for a cheaper FPGA-based time digitizer solution, best suited to the main spectrometer's straw chambers reduced intrinsic time resolution, or the use of continuously digitizing flash ADCs for the electro-magnetic (LKr) and hadronic (MUV1, MUV2) calorimeters, which still use TEL62 boards for L0 trigger primitive generation.

## 4.1. TEL62 hardware

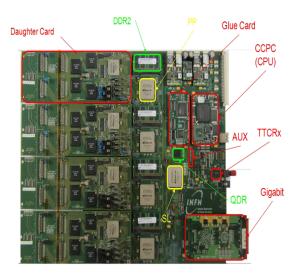

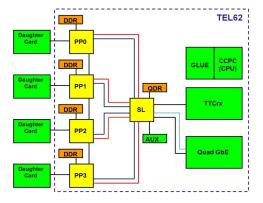

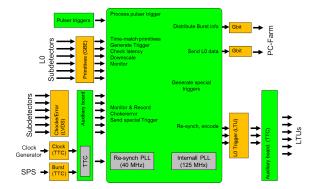

The TEL62 board (fig. 1) has a similar overall architecture to the TELL1 board developed for the LHCb experiment[10], but is based on much more powerful and modern devices, resulting in more than four times the processing power and more than twenty times the buffer memory of the original, with several other improvements in terms of connectivity. Overall, about 100 TEL62 boards were produced, most of them being actually installed in the experiment. The architecture of the TEL62 is shown in fig. 2.

Each of 4 FPGAs<sup>14</sup> (Pre-Processing or "PP-FPGA"), is connected to a daughter card through a high density Samtec 200-pin connector, and to a 2 GB DDR2 memory buffer (in SO-DIMM form factor) which stores data during the L0 trigger latency. Each PP-FPGA is also connected to its neighbour(s) by two uni-directional 16-bit buses, which can be used for daisy-chaining.

A central FPGA of the same type (Sync-Link or "SL-FPGA"), is connected to each PP-FPGA by two inde-

Figure 1: TEL62 board equipped with four TDCBs.

Figure 2: TEL62 block diagram.

pendent 32-bit data buses, for data and L0 trigger primitive flows respectively; each bus runs at 160 MHz and all signal lines are equal in length. The data and L0 trigger primitives from all PP-FPGAs are merged on the SL-FPGA, then formatted and stored in buffers: that for data is based on a Quad Data Rate (QDR) synchronous dual-ported SRAM, whose high bandwidth allows simultaneous read and write operations. With a 16-bit bus at double data rate and 100 MHz clock frequency, a bandwidth of 3.2 Gbit/s is reached. The chosen QDR device<sup>15</sup> has a depth of 1 MB.

The SL-FPGA is also connected by another 120 MHz bus to an output daughter card, through which data is eventually sent to other parts of the TDAQ system. The

$<sup>^{13}\</sup>mathrm{The}$  latter two being also read-out by the calorimeter system.

<sup>&</sup>lt;sup>14</sup>Altera Stratix<sup>®</sup> III EP3SL200F1152C4 with 200,000 logic elements and 9 MB embedded memory.

<sup>&</sup>lt;sup>15</sup>Samsung Semiconductor K7Q161852A-16.

default output card is a custom quad-Gigabit Ethernet card (Quad-GbE) [12] developed for the LHCb experiment, which implements  $^{16}$  4  $\times$  1 Gbit copper Ethernet channels.

The slow control, monitoring and configuration of the TEL62 is handled by 2 more daughter cards inherited from the TELL1 design: a commercial Credit-Card PC (CCPC) running Linux<sup>17</sup> and a custom I/O interface card ("Glue Card") connected to the CCPC through a PCI bus. Three different communication protocols are implemented on the Glue Card and distributed to all devices and connectors on the TEL62: JTAG, I2C and ECS. JTAG is used to remotely configure all the board devices, I2C is mainly used to access registers on some daughter cards, while ECS is a custom protocol used to access the internal registers of the PP- and SL-FPGAs via a 40 MHz 32-bit bus.

The 40 MHz experiment clock and the L0 trigger information are distributed to TEL62 boards through a CERN-standard optical TTC link. The TEL62 uses a TTCrx chip to decode the clock and trigger information. The clock signal is sent to the SL-FPGA and distributed from there to the PP-FPGAs through internal PLLs that upscale it by 4 and set the correct phase to correctly latch incoming data. A further layer of communication is provided by an auxiliary connector, which can be used to plug in an inter-communication card for daisy-chaining several TEL62 boards (section 5.3.1).

The board size complies with the 9U Eurocard standard (340 x 400 mm). It gets power from a VME-like connector (not used for communication) compatible with that of the TELL1. Overall power consumption of the TEL62 board is around 50 W. The printed circuit is made of 16 layers, with all lines controlled in impedance (50  $\Omega$ ). Special care was taken in routing the clock tree, to minimize time jitter, and in equalizing the lengths of data bus lines.

## 4.2. Common TEL62 firmware

Appropriately for a multi-purpose TDAQ board, a large part of the firmware design is common to all TDC-based sub-systems and is described in this section, while sub-detector specific parts are detailed in subsequent sections.

The common part of the firmware consists of about 65,000 user-written lines of VHDL code. The firmware

is hierarchically managed with common and subdetector specific libraries through the Mentor Graphics HDL Designer<sup>®</sup> software suite, interfacing to the Altera Quartus II<sup>®</sup> compiler, and to the Apache Software Foundation SVN<sup>®</sup> versioning system, with a central repository allowing concurrent development by the various institutions participating in the project.

Multiple clocks are used within the firmware, with most of the modules running on a 160 MHz main clock, locally generated inside each FPGA and phase-locked to either the common experiment-wide 40 MHz master clock received from the TTC (the SL-FPGA) or to a 40 MHz clock distributed by the SL-FPGA (each PP-FPGA, with programmable individual phase-adjustment). Clock frequency constraints for some external devices make the use of different clock domains within FPGAs unavoidable, and care had to be taken in order to control timing-closure violations.

The UDP protocol was chosen as a light-weight solution for output data transmission over the GbE links, allowing direct connection to a standard switched network. This choice was dictated by requirements of simplicity and high throughput. To deal with the unreliable UDP protocol, which has no re-transmission, extensive error detection was implemented.

Quite extensive test and debugging features are implemented in the firmware, as required to control a rather complex system. These are similar within all FP-GAs and include, besides a large number of user accessible registers and the capability to read and write internal buffer memories and FIFOs by the CCPC, the presence of a "freeze" logic to halt all processing, which can be triggered by the occurrence of programmable conditions (errors, timestamp counts, buffer filling, etc.). A distributed "logging" system is implemented as a shared internal memory to which most firmware modules can write a variable number of timestamped data words to report the occurrence of specific conditions. Such memories can be read by the CCPC, and their use, by selectively masking through registers the firmware modules and message severity levels which to be logged, was very useful during commissioning, to monitor and understand rare/anomalous conditions.

Configuration, slow control and monitoring of the board (and its daughter-cards) is performed by the CCPC. A versatile management program with command-line interface and extensive scripting and macro capabilities was developed, and is used for all communication with the board; it consists of about 55,000 lines of C code, interfacing to low-level hardware libraries. An interactive version is used for testing and monitoring, while during data-taking the program

<sup>&</sup>lt;sup>16</sup>Using the Intel IXF1104 as Media Access Control and Marvell Alaska 88E1140 as physical controller devices.

<sup>&</sup>lt;sup>17</sup>CERN Scientific Linux 4 [13].

runs as a daemon and communicates through DIM with the TDAQ control system for board configuration, error checking and monitoring.

#### 4.2.1. PP-FPGA logic

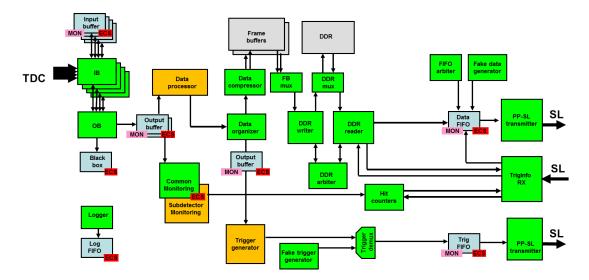

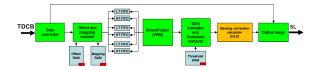

A schematic of the common PP-FPGA firmware (the same for all four devices) is shown in fig. 3. The common PP-FPGA logic is configured by more than 100 32-bit registers, and most of it runs on a 160 MHz clock.

Each PP-FPGA handles data received from a daughter-card, which in the case of TDCBs arrives as independent 32-bit parallel data streams from each of four TDC chips. The data from each TDC chip is stored into dedicated 2K word deep Input Buffer (IB) FIFOs, and monitored on-the-fly in order to identify corrupted data, parity errors, malformed data frames or repeated words. These issues indicate upstream errors, and cause appropriate error flags to be set and later transmitted together with the data. The IBs act as de-randomizing storage and provide the input to the following merging stage; the latter patches together the individual TDC data words belonging to the same  $6.4 \mu s$ -long data frame (identified by a leading timestamp word) and produces a merged data frame with updated word count field, to be stored into a 2K word deep Output Buffer (OB) FIFO. A copy of the merged data is written into another identical buffer feeding data monitoring modules. Furthermore, half of the OB data is constantly available in a circular buffer accessible from ECS, useful for post-mortem debugging in case a fatal error condition triggers the freeze logic.

After an optional sub-detector specific data processing module, meant for data calibration, remapping or processing to be performed on-the-fly, data frames are passed to a Data Organizer (DO) module. The DO unpacks data from each time frame and arranges them into 256 time-ordered slots, each time slot being 25 ns long.

The large L0 trigger latency and high data rate (which is sensitive to beam rate fluctuations) require a sizeable amount of internal RAM devoted to storing data in the 256 time slots belonging to each data frame. Moreover, in order to cope with the continuous data flow without introducing any dead time, two identical memories (32K words each) are used, so that one time frame is unpacked while the previous one is being processed by the following firmware modules.

The Data Compressor (DC) module compacts the data for one  $6.4 \mu s$  time frame, allowing a variable number of words in each 25 ns time slot, in order to optimize its storage into the external memory, thus minimizing the required number of accesses when data is written and read back from it.

Such external DDR memory is organized into 64 million 256-bit wide locations per PP-FPGA. Half of the memory space is used as a circular buffer to store data for 131,000 data frames, a latency in excess of 800 ms before overwriting, each frame allowing up to 2K 32-bit words, corresponding to a 80 MHz rate of data words from a single TDC chip (which can steadily produce slightly less than 40 MHz of data words at most). The other half of the DDR memory is used to store the information about the dynamically defined starting address and number of data words for each 25 ns time slot: addresses for up to 1 billion time slots are stored, corresponding to 26.8 s worth of data.

Access to the DDR memory occurs in pages of up to 32 256-bit words, through an ALTERA proprietary firmware driver running at 320 MHz, which takes care of memory refresh operations, while arbitration between the periodic data frame writing process (6.4  $\mu$ s period) and the aperiodic reading process (at the L0 trigger rate, up to a maximum of once per  $\mu$ s) is taken care of by the firmware. The CCPC can also access indirectly the DDR memory in blocks of 1 kB, for test or debugging purposes.

The sub-detector-specific Primitive Generator modules (for sub-detectors participating to L0 trigger generation) also receive a copy of the frame-merged and time-ordered data from the DC, through a dedicated 2K word deep Trigger Input Buffer (TIB), and they process it on-the-fly to produce L0 trigger primitives; such modules are described in section 6.

Upon reception of a readout request from the SL-FPGA (corresponding to a L0 trigger) each PP-FPGA sends the formatted data corresponding to a programmable time window around the trigger time to the SL-FPGA. The PP-FPGA reads the relevant trigger information (25 ns trigger timestamp and 6-bit trigger type) from a dedicated trigger information FIFO, and the Trigger Information Receiver (TRIGINFORX) module handles it accordingly. For triggers involving real data (such as "physics" triggers) the DDR Reader module receives the trigger time stamp and the (programmable, possibly depending on trigger type) number and offset (with respect to the trigger time) of the time slots to be read; it reads from the DDR the corresponding data, which is formatted and written in the 2K word deep final data FIFO buffer. For special triggers (for which actual TDC data is not required) the TRIGIN-FORX fills the final data FIFO itself. In the case of End Of Burst triggers, write access to the final data FIFO is granted to other firmware modules, such as a hitcounting module and other sub-detector specific modules, which sequentially append their monitoring data.

Figure 3: Schematics of the common firmware in the TEL62 PP-FPGAs. Buffers whose filling is continuously monitored to act on flow control are labelled "MON". Buffers which are accessible by the CCPC for monitoring and debugging purposes are labelled "ECS".

The data is then moved from the final data FIFO to the SL-FPGA, with checks on parity and event size.

Both the data and L0 trigger primitive paths from PP-FPGA to SL-FPGA can be tested using data words produced by embedded pseudo-random bit sequence generators; this allows the best relative phase delay between the two FPGA clocks for error-free communication to be determined, as such delay can vary depending on the actual version of the firmware loaded into the FPGA, due to the internal routing of the logic by the compiler. Overall, the common part of the firmware uses 55% of the PP-FPGA logic resources and 45% of the internal memory.

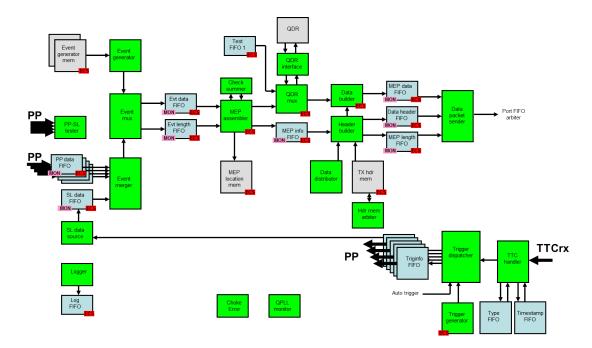

#### 4.2.2. SL-FPGA logic - data

The SL-FPGA logic handles two separate data flows: one for the main event data being read after a L0 trigger and sent to the PC farm, and one for the L0 trigger primitives being continuously produced and sent to the L0TP, the latter being present only for sub-detectors participating to L0 trigger generation.

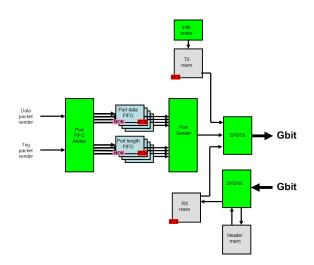

The main data flow is described first and is shown schematically in fig. 4. The non-subdetector-specific SL-FPGA logic is configured by about 150 internal 32-bit registers; the logic mostly runs on a 160 MHz clock, except for the interface to the output GbE links which is limited to 120 MHz by the external devices, thus requiring separate clock domains.

The first part of the SL-FPGA logic merges event data, which was received from the four PP-FPGAs and stored in 2K word deep FIFO buffers, together with lo-

cally produced data, and stores the complete event into a buffer FIFO. For testing purposes fake events can be read from an embedded RAM instead.

The MEP Assembler module arranges events into Multi Event Packets (MEPs), containing a programmable number of events, in order to optimize network transmission bandwidth. The module formats the data, while also computing and appending a CRC checksum to verify integrity at later stages. MEPs are then stored into the external QDR memory arranged as a circular buffer, where they lie waiting for further encapsulation and transmission. The location of the most recent 256 MEPs is recorded in a dedicated memory for *post-mortem* debugging.

The following Packet Builder stage extracts MEPs from the QDR memory and encapsulates them into network packets, by adding the UDP, IP and Ethernet protocol headers. Jumbo Ethernet frames are supported, as well as IP fragmentation. All sub-detectors must send data fragments corresponding to the same event to the same PC of the PC Farm: this requires event distribution to be fully coherent among all sub-detectors, and has implications on the number of events stored in a MEP, the number of output GbE ports used and the packet addressing to farm nodes. A flexible three-level round-robin distribution mechanism for MEPs is implemented. Each of the four TEL62 GbE ports has a list of up to 63 programmable destination IP addresses over which it cycles, and a programmable number of MEPs is sent to one port before switching to the next one. Independently from the above cycle, the destination address

Figure 4: Schematics of the common firmware for the data path in the TEL62 SL-FPGAs. Buffers whose filling is continuously monitored to act on flow control are labelled "MON". Buffers which are accessible by the CCPC for monitoring and debugging purposes are labelled "ECS".

for the current port is changed to the next one in the list after a (distinct) programmable number of MEPs is sent.

The following part of the logic, shown in fig. 5, is shared by both the main event data and the L0 trigger primitive flows. Each of the four output GbE ports can be configured to be dedicated to either of the two flows.

Figure 5: Schematics of the common firmware for the output section of the TEL62 SL-FPGAs. Buffers whose filling is continuously monitored to act on flow control are labelled "MON". Buffers which are accessible by the CCPC for monitoring and debugging purposes are labelled "ECS".

Formatted packets destined to a given output port are stored into 8K word deep buffer FIFOs (one per port), allowing to decouple the flow from any temporary congestion of individual hardware links. The Port Sender module actually transfers the packets to the Quad-GbE card (whose input interface is shared by all ports) in an order which depends on the current availability of a port. Dedicated modules allow using the output links to either transmit pre-programmed data from an internal memory, or to store the data received from the output links when configured in mirroring mode, and are used for board tests.

The logic to handle L0 triggers comprises a TTC Handler module which timestamps the triggers received from the TTC network and stores them into a FIFO buffer, similarly storing trigger type words and pairing them with the corresponding trigger timestamp values according to their order of arrival. Triggers are then delivered to each PP-FPGA by the Trigger Dispatcher module. Debugging and test features include a circular buffer storing the last 256 triggers dispatched, the possibility to autonomously generate triggers when specific primitive data word patterns are recognized, and preprogrammed trigger sequences under CCPC control.

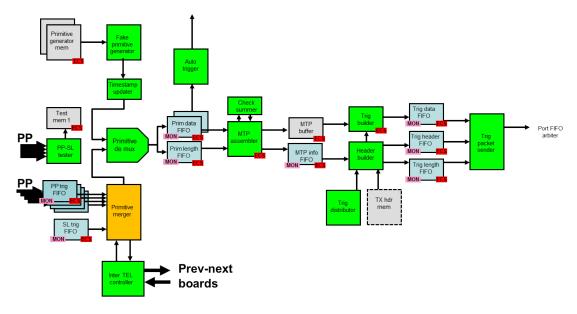

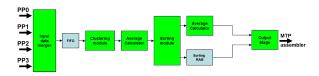

#### 4.2.3. SL-FPGA logic - L0 primitives

For sub-detectors involved in L0 trigger generation, the flow of L0 trigger primitives proceeds in parallel to the main data flow, and is shown schematically in fig. 6. Overall, the common part of the firmware uses 20% of the SL-FPGA logic resources and 35% of the memory.

Primitive fragments from enabled PP-FPGAs are merged by a sub-detector-specific module. Fake primitives can be generated within the SL-FPGA for test purposes, being read from a dedicated memory and with their sequential number and timestamp being changed on-the-fly to resemble real primitives. Merged primitives are then aggregated into Multi Trigger Packets (MTPs) by the MTP Assembler, and temporarily stored in an internal 4K-word deep circular buffer: the smaller size of primitives, with respect to event data, does not require the use of a large external memory device. MTPs can either contain a fixed number of primitives (with a time-out mechanism to avoid excessive latency accumulation) or can be sent at periodic time intervals  $(6.4 \,\mu\text{s} \text{ period})$ , which is the normal working mode required by the LOTP (see section 9). As for the main data flow, the Trigger Builder and Sender modules handle the preparation of UDP packets and their transmission to the output links through the dedicated port buffers. A test feature allows selectable trigger primitives to autonomously generate L0 triggers locally, to be used when the LOTP is not available.

#### 5. TEL62 daughter cards

Each TEL62 can host up to 4 daughter-cards, providing input data to be handled by the corresponding PP-FPGAs; while the TELL1 daughter-cards developed for LHCb are mechanically compatible with the TEL62, different cards were developed for NA62 to provide time measurements on digitized detector-signals (section 5.1), or to handle digital pulse-height information from calorimeters (section 5.2). Data output is provided by another daughter-card, which can be either the Quad-GbE card described in section 4.1, or a transmitter card based on a custom protocol (section 5.2). Furthermore, inter-connection cards were developed to allow TEL62s to share data among themselves (section 5.3.1).

## 5.1. TDC boards

Most sub-detectors in NA62 exploit their good time resolution in order to cope with the high-rate of events: a time-digitizer card (TDCB) was developed to handle time information [15]. Overall, more than 130 TDCB

were produced, most of them being actually installed at the experiment.

The design of the TDCB was driven by the desire to integrate a large number of channels on a single card, in order to ease trigger generation. The quest for a compact and common electronics, and the relatively short distance between sub-detectors and a site where readout electronics could be placed (in absence of severe space constraints), led to the choice of having digitizers on the readout board itself. This left only analogue (and sub-detector specific) front-end electronics on each sub-detector in a potentially higher radiation environment, with most clocked digital components being close together, at the price of transmitting the pulses to be time-digitized over O(5 m) long LVDS cables. The requirements of a good time resolution and high channel integration led to the choice of the CERN High-Performance Time-to-Digital Converter [14] (HPTDC) as time digitizer.

Each HPTDC works in fully digital mode and hosts 32 TDC channels when operated in high-resolution mode (100 ps LSb), with some internal channel buffering for multi-hit capability and a trigger-matching logic allowing the extraction of hits in selected time windows. Channels are arranged in groups of 8 sharing some internal buffers. While trigger-matching mode was implemented to allow the chip to act as front-end buffer, by storing digitized data while a trigger signal is generated, in NA62 the L0 trigger latency was chosen to be much longer than the maximum storage time allowed by the HPTDC before internal timestamp roll-over (51.2  $\mu$ s), in order to allow complex trigger decisions to be performed at the lowest trigger level. Moreover, in NA62 the L0 trigger is computed based on the acquired data itself. For these reasons, the HPTDC is used in triggermatching mode just as a way to obtain properly timeframed data from it, as explained in the following section.

Four HPTDC chips are mounted on each TDCB, for a total of 128 channels (512 channels per fully-equipped TEL62 carrier board); all TDC channels for most small sub-detectors are thus hosted on a single TEL62 board, and the entire 2000 channels of the RICH sub-detector are managed by just 4 TEL62s. The measurement of both the leading and trailing edge times allows analogue pulse-height information to be obtained by a time-over-threshold method, and HPTDCs can indeed be programmed to digitize the time of occurrence of both signal edges, provided they exceed a 7 ns time separation.

The TDCB houses four 68-pin VHDCI connectors for input signals, each of them delivering 32 LVDS signals to one HPTDC, with two spare pairs being used to

Figure 6: Schematics of the common firmware for the L0 trigger primitive path in the TEL62 PP-FPGAs. Buffers whose filling is continuously monitored to act on flow control are labelled "MON". Buffers which are accessible by the CCPC for monitoring and debugging purposes are labelled "ECS".

provide additional grounding and to allow user-defined back-communication from the TDCB to the front-end electronics. This latter feature can be used to trigger the injection of calibration pulses in a sub-detector or calibration patterns in its front-end electronics. The connection between front-end and TDC chips can use standard SCSI-3 cables, or higher-performance ones if needed.

The TDCB houses a dedicated FPGA<sup>18</sup> named TDC Controller (TDCC-FPGA) which handles the configuration of the four HPTDCs, reads the data they provide, and optionally pre-processes it. A 2 MB external static RAM block is also present, and can be used for on-line data monitoring purposes and low-level dataquality checks. The TDCC-FPGA can be configured by an on-board flash memory or through JTAG (either using a JTAG port on the TEL62, or its embedded CCPC processor). Communication between each TEL62 PP-FPGA (section 4) and the corresponding TDCC-FPGA proceeds through a 200-pin connector hosting four independent 32-bit single-ended LVTTL parallel data buses (one per HPTDC) and dedicated lines for synchronous commands and resets. The TDCC-FPGA can also be accessed from the CCPC on the TEL62 board via a dedicated I2C connection for slow operations, such as access to internal configuration registers. The HPTDCs are configured via JTAG, with the TDCC-FPGA acting as the JTAG master: configuration data is sent to the TDCC-FPGA from the CCPC via I2C, and is then uploaded to the HPTDCs. Alternatively, both the TDCC-FPGA and the four HPTDCs can be inserted into a global JTAG chain, which also includes all TEL62 devices and can be driven by the CCPC.

The TDC contribution to the time resolution depends on the random jitter of the reference clock against which the measurement is performed. The master 40 MHz clock is distributed via the TEL62 to the TDCBs, where it can be configured to be processed by two more jitter-cleaning stages: an on-board QPLL and the internal PLL of the TDCC-FPGA. Detailed tests performed in different configurations showed that the level of the jitter, measured with Time Interval Error (TIE) at 50% level, is below 20 ps.

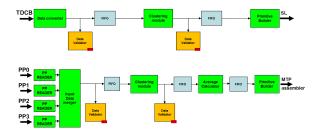

## 5.1.1. TDCB firmware

The firmware for the TDCC-FPGA is common to all sub-detectors. The HPTDC chips are configured to run in high-resolution mode (100 ps LSb), usually generating two 32-bit words per input signal, with 19-bit leading-edge and trailing-edge time digitization.

HPTDCs are used in trigger-matching mode, storing measurements in internal buffers, from where those with times around a "trigger" signal can be later extracted. However, such working mode is only used as a way to obtain properly time-framed data, and extraction is periodically driven by the TDCC-FPGA with no relation to the L0 trigger. The HPTDC time-matching

<sup>&</sup>lt;sup>18</sup>Altera Cyclone<sup>®</sup>III EP3C120F780 with 120,000 logic elements.

extraction parameters are thus set to read-out all hits which occurred since the previous extraction. This results in reading all hit data (only once), while overcoming the limited time-digitization range of the HPTDC, with the TDCC-FPGA appending a timestamp to each data frame, unambiguously associating each hit to an "absolute" time since the beginning of the burst. With the chosen frame period of 6.4  $\mu$ s and a 400 ns LSb, the range of the 28-bit frame timestamp word exceeds the maximum duration of a burst.

The TDCC-FPGA independently processes data from each of the four HPTDCs through a dedicated 32-bit bus using a block-write protocol, reading one data word every 25 ns. It formats data into timestamped frames, also adding a trailing word-count, as well as optional error words in case anomalous data or conditions are detected. Two redundant chip identifier bits in each hit word are replaced with parity bits to allow off-line data integrity checks. Besides handling HPTDC configuration, the TDCC-FPGA JTAG master controller is also used to read status information during running.

Several test and debugging features are present in the firmware. Two different TDC data emulators are implemented: one generates programmable repeating patterns on selected channels, and another cyclically transmits pre-loaded data words from internal memory buffers. The latter is used during the TEL62 acceptance test, using specific patterns to stress the boards by emulating different detector rate conditions. A fraction of the TDC data stream can be stored into the board static RAM during running, from where it can be accessed at the end of a burst for debugging and monitoring purposes. The TDCC-FPGA can drive a spare output LVDS line of each HPTDC input cable to trigger the front-end boards for sub-detector calibration: front-end boards can inject signals into the TDC chips in response to such stimuli, thus allowing a test of the whole chain. Such calibration can be driven periodically by a programmable counter or upon command from the TEL62 carrier board.

# 5.2. Calorimetric trigger boards

The calorimetric L0 trigger works on digitized pulseheight data, from the digital sums of  $4 \times 4$  cells ("supercells") of the electromagnetic liquid krypton calorimeter (LKr), and single-channel data from other calorimetric sub-detectors.

The calorimetric trigger processor is a parallel system, composed of TEL62 boards configured as Front-End, Merger and Concentrator devices with different functions:

• Front-End boards receive digital sums from the

calorimeter digitizing modules, and perform peak searches in space to determine the time, position and energy of each detected peak;

- Merger boards (only used for the LKr) receive trigger data from the Front-End boards and merge peaks into clusters:

- The single Concentrator board receives peaks or clusters from the calorimetric sub-detectors, counts them, computes separate sums for electro-magnetic and hadronic energy, and generates trigger primitives.

In order to handle the 864 LKr super-cell channels (plus the 20 channels from other sub-detectors), 37 TEL62 boards are used, for which several daughter-cards were developed: receiver cards (TELDES) are used for receiving input data, and paired transmitter (Cal-L0TX) and receiver (Cal-L0RX) cards are used to pass information between the TEL62s, in a tree structure. Additional daughter cards are used to allow the coarse-grained input data used by the calorimetric L0 trigger to be sent to the PC farm, where it can be used for HLT processing.

The calorimetric L0 trigger mostly uses a dedicated firmware for TEL62 FPGAs: more details will be made available elsewhere.

#### 5.3. Auxiliary cards

A few more daughter-cards were developed for the TEL62, used for specific purposes.

#### 5.3.1. Interconnection card

For sub-detectors with more than 512 channels using TDC boards, the information is necessarily split over more than a single TEL62 board. In order to allow triggering algorithms that require to correlate data from the whole sub-detector, a bi-directional communication card was developed.

InterTEL cards (fig. 7) provide a daisy-chain link between different TEL62s [24, 25]. They are connected to the carrier board by a 60-pin fine-pitch SMD connector, with buffered signals to reduce interference, noise, and cross-talk issues. The InterTELs are connected to each other via two RJ-45 connectors (one for TX and one for RX), with a LVDS bus for the physical layer and a proprietary serial communication protocol for the data link layer.

The protocol is implemented by serializer/deserializer chips<sup>19</sup> separately clocked at 40 MHz. The data transmission rate of the link is 720 Mbps, including an overhead of 80 Mbps due to the embedded clock

<sup>&</sup>lt;sup>19</sup>Texas Instruments DS92LV16.

Figure 7: InterTEL board top (left) and bottom (right) views.

foreseen by the protocol. The actual throughput is then 640 Mbps. One twisted-pair of a Cat. 6 S/FTP 26-AWG cable is used, and a specific chipset<sup>20</sup> is used to extend the maximum allowed cable length, so that the allowable 6 dB total link loss corresponds to 85 m.

## 5.3.2. Pattern generation card

A TEL62 daughter-card named PATTI, with level translators and VHDCI connectors was developed to implement a versatile digital pattern-generation system compatible with TDCBs, required for extensive system debugging and production testing. A dedicated PP-FPGA firmware controls the card, which can generate 128 LVDS signals in periodic patterns, or in a fully customizable way by reading individual channel data from an internal memory. The signal edges can be controlled to 6.25 ns precision. In order to provide a fully self-contained test system, the card also provides a trigger output to emulate L0 triggers with no need for a dedicated LTU board (section 3.1), as well as CHOKE/ERROR signals for test purposes. The PATTI board has the same format as the TDCB, and up to four can be housed on a TEL62, for a total of 512 output channels over 16 SCSI-3 cables.

#### 5.3.3. Multi-purpose card

Another TEL62 daughter-card named TALK was produced to interface parts of the old readout system of the NA48 experiment to the new TDAQ system during the first phase of NA62. The card works as a multipurpose interface between a TEL62 and external devices: it houses the same FPGA used on the TDCB, one bipolar encoder/transceiver "Taxi" chip, 5 GbE links, 5

LEMO I/O connectors, 4 RJ-11 connectors and a multipin connector for the LTU card. The card is usually controlled from the TEL62 through dedicated parallel buses, but can also be accessed through dedicated JTAG and I2C connectors, and Ethernet as well. The TALK board is twice the size of the TDCB, and up to two can be housed on a TEL62; a 6U VME frame was also developed for standalone use. Besides its original use, it was successfully used as a L0TP emulator and calibration control system.

#### 6. TDC-data L0 trigger logic

As mentioned, L0 trigger primitives are sent in Multi Trigger Packets (MTPs), transmitted periodically for every 6.4us time frame, even if the MTP contains no primitives. Each primitive is coded into a single 32-bit word containing its ID (i.e. the conditions which are satisfied), the 8 least significant bits of its 25 ns timestamp, and 8 fine-time bits (down to the 100 ps unit), thus identifying the primitive time up to 6.4  $\mu$ s. The upper part of the timestamp, to cover the full duration of the burst, is stored in the header of each MTP. Up to 256 time-ordered primitives are stored in an MTP. For the expected event rate at full beam intensity, the average maximum of 80 primitives per frame results in packets well below standard Ethernet payload limits. The corresponding average bandwidth is significantly less than 1 Gb/s even for the most active sub-detector: even allowing for rate fluctuations, at most one GbE link is used for MTPs, leaving three available for main readout data.

The L0 trigger primitive generation firmware is implemented in the TEL62 FPGAs, which also contain the common logic to handle the data flow and L0 trigger response (section 4.2). Sub-detector channel data are correlated first in the PP-FPGAs (dealing with one TDCB each) and later in the SL-FPGA (dealing with the entire board). A third layer of correlation logic might be implemented in the SL-FPGA in case more TEL62s are connected in a daisy chain, for sub-detectors with more than 512 TDC channels involved in the L0 trigger (section 5.3.1).

# 6.1. NA48-CHOD and RICH L0 trigger

The purpose of this firmware[23] is to produce clusters of hits belonging to the same event based on the hit times, providing a precise time reference and a hit count. No detector-specific information is used so that the firmware can work for different sub-detectors, such as RICH and NA48-CHOD. The main guidelines for the design were the minimization of resource usage and

<sup>&</sup>lt;sup>20</sup>Texas Instruments DS15BA101 and DS15EA101.

a stable latency for production of the primitives. The capability to cope with the full expected hit rate while maintaining as much versatility as possible were also followed as guidelines. The firmware was designed to be reliable, adaptable to any primitive-generating subdetector, easily upgradable, and compatible with the InterTEL board (section 5.3.1).

Between 2016 and 2018 the L0 trigger primitive generation for the RICH, which has 2000 TDC channels distributed over 4 TEL62s, did not use inter-connected boards. Analogue sums of 8 channels available from the RICH front-end electronics were used, digitized in a fifth dedicated TEL62 board.

In the PPs a preliminary clustering is performed. In the SL, clusters coming from the 4 PPs are merged, then used to generate the L0 trigger primitives. The FPGA resources usage for the common logic (sec. 4.2) plus this L0 trigger logic amounts to 75% (45%) of the available logic elements and 47% (44%) of the available memory for the PP- (SL-)FPGA.

A common 32-bit data format ("RICH format") is used to optimise the design efficiency: each firmware module uses such format for input and output, allowing to easily add, delete or reuse modules within the project. This format includes two kinds of paired 16-bit words, each identified by a 2-bit word ID: cluster words and timestamp words. The choice of 16-bit words is made to match the bus width of the InterTEL board (section 5.3.1).

Cluster words identify clusters of hits and contain: a 12-bit fine-time (T) representing the time of the cluster in units of 100 ps; a 8-bit hit multiplicity (N) indicating the number of hits of a cluster; a 8-bit cluster time sum (S), which is the sum of the time differences between the cluster's "seed" time and the times of individual hits belonging to the cluster. S is used to efficiently compute the weighted average of the cluster hit times, and is a signed number whose value remains small even for clusters with a large number of hits.

Timestamp words contain a 28-bit word with 400 ns LSb, with the most significant digits of the global experiment time. There are 16 timestamp values in each  $6.4 \,\mu s$  time frame. In case there are no hits corresponding to a given timestamp, a fake cluster with N=0, S=0 and the maximum possible T is generated. Such clusters are called *speed-data* and are used to control the firmware latency, while they are ignored by all modules.

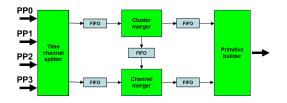

## 6.1.1. Overall L0 trigger logic

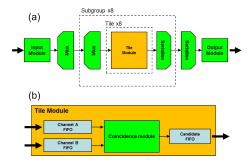

Fig. 8 shows the block diagrams for PP- and SL-FPGA firmware; the clock frequency is 160 MHz for

all modules. Primitives produced by the firmware represent time clusters of hits belonging to the same event.

Figure 8: PP- (top) and SL-FPGA (bottom) RICH/NA48-CHOD firmware block diagrams.

In the initial stage of the PP-FPGA firmware the TDCB hits are formatted into clusters with N=1, S=0, and T is set as the hit time. Such clusters are time-sorted at the 25 ns level, i.e. using the 4 most significant bits of T. Data Validator (DV) modules check the consistency of the data format throughout the firmware: all timestamps and cluster data words must be sorted at the 25 ns level, and after a timestamp there must be at least one data word. If an error occurs a flag is set, and it has to be delivered in the EOB packet. The following Clustering Module (CM), discussed in detail in section 6.1.2, merges clusters, which are then sent to the SL-FPGA by a Primitive Builder (PB) module.

In the SL-FPGA, the Data Merger (DM) module merges the clusters coming from the 4 PP-FPGAs and potentially of the InterTEL boards. It reads data at a rate of 1 word per clock cycle, preserving the 25 ns time ordering and skipping timestamps and speed-data. The module consists of 3 identical sub-modules organized in a two-level tree structure: each of the two branches merges the data from two of the PP-FPGAs, while the root merges the data from the branches. When using InterTEL boards, a 3-level DM structure can be implemented. Each module is purely combinatorial, with a FIFO buffer both on the input and on the output. Special care was taken to reduce the length of the paths and the number of combinatorial levels in each module. DM sub-modules start working only if both input FIFOs are non-empty. This could lead to starvation of data in the FIFOs, e.g. when one PP-FPGA receives hits from TD-CBs faster than others. Speed-data words are used to avoid starvation: since each PP-FPGA produces at least 16 clusters per time frame, FIFOs cannot be empty for long periods of time. The T value of speed-data is set to the maximum possible value in order to give priority to real data in the DM.

After another Clustering Module, the Average Calculator (AC) module computes the weighted mean of the

clusters' times: T is increased by the S/N ratio and S is then reset to zero. The S/N ratio is computed with a 8-bit FPGA-embedded divider. Finally the SL-FPGA Primitive Builder (PB) formats the incoming data in the standard NA62 MTP format, computes the ID for each primitive and sends it to the standard MTP assembler module.

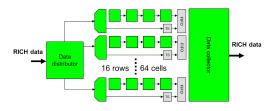

## 6.1.2. L0 clustering module

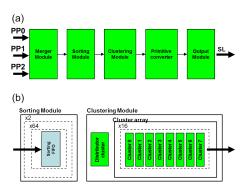

The CM consists of sub-modules, as shown in fig. 9. It merges clusters of hits or of other clusters that are closer in time than a programmable value. The comparison is performed only on T, while S and N are only taken into account after the comparison of T has been made.

Figure 9: Block diagram for the RICH/NA48-CHOD L0 clustering module.

The Data Distributor (DD) module feeds the incoming data into so-called clustering rows. There are 16 rows, each made of 4 cells and a time slot (TS) register. Each row elaborates input hits belonging to a specific 25 ns time slot. By construction, a row can handle up to 4 clusters per 25 ns time slot. Any cluster beyond the fourth is discarded, and an error flag is set, to be sent in the EOB packet. Each cell consists of a comparison module, an embedded 18-bit multiplier and a correction module, all interconnected by FIFOs.

The DD rearranges data into fine-time and TS, sending the former to the cells and the latter to the TS register of the proper 25 ns row. The DD is designed to send each hit into one of two adjacent rows (rows 15 and 0 are considered adjacent), depending on the time of the hit, and hits belonging to the same event which happen to be split over two adjacent 25 ns time slots can be merged together. All the computations within the cell are done on 9 bits: 8 bits for *T* and 1 more bit to handle adjacent 25 ns time slots.

The comparison of the T values and the cluster merging are performed by the cells: each cell initially stores the first received hit or cluster as a seed and defines a new cluster with  $T_s$ ,  $N_s$  and  $S_s$  values in input. If the  $T_i$  value of an incoming cluster matches the stored  $T_s$  within a programmable time window,  $N_s$  and  $S_s$  are updated:  $N_s = N_s + N_i$ ,  $S_s = S_s + (T_i - T_s)N_i$ . If  $T_i$  does

not match  $T_s$ , the incoming cluster is passed to the adjacent cell, which performs the same operations. If such cluster has a  $T_i$  that is greater than  $T_s$ , the receiving cell increases an internal time-position field that will be used to time-order the clusters.

The  $n^{\text{th}}$  row can be read out when the  $(n+2)^{\text{th}}$  row is being filled: this is done by *flushing* the row. Cells act as a shift register, writing the time position register and the  $T_s$ ,  $N_s$  and  $S_s$  of the stored cluster to the row output FIFO. In order to keep the firmware data throughput at 1 word per clock cycle, the flushing of a row must be completed before the row needs to be filled again. The output latency  $L_o$  of a cluster is given by  $L_o = 2d + f + m$ , where d is the number of cells per row, f is the delay of the output FIFO and m is the latency of the cell multiplier. In our case,  $L_o = 2 \cdot 4 + 3 + 3 = 14$ . The number of rows must be greater than  $L_o$ , and was set to 16 so that there will always be a free row to fill.

Finally, the Data Collector (DC) module retrieves data from the rows' output FIFO and converts them into the RICH format. The DC module is divided into four parts. The first one reads the data from the rows, being able to switch between rows without missing a clock cycle. The second part sorts the clusters of a row by addressing RAM blocks with the time position field of the clusters. After the sorter, clusters with hit multiplicity outside a programmable range are discarded: this allows to reduce the noise related to events with too low or too high hit multiplicity. The fourth part of the DC reads the sorted remaining clusters and converts them to the RICH format.

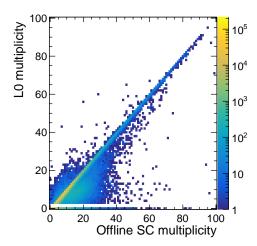

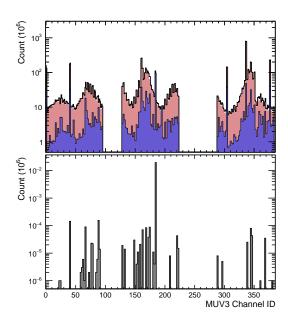

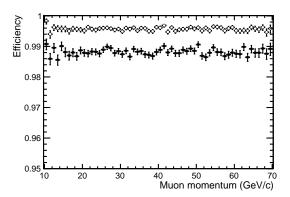

## 6.1.3. Test and performance

The design was simulated and implemented in the actual system since the beginning of the 2016 physics run. Data triggered by other sub-detectors were analysed and compared to the output of the RICH firmware, in order to check its behaviour. The analysis isolates the events in the RICH detector, computing their time and hit multiplicity. Fig. 10 shows the high correlation between the hit multiplicity computed in the off-line analysis and by the on-line RICH L0 firmware. The module inefficiency is computed by considering all events that have zero L0 hit multiplicity but non-zero analysis multiplicity, and is measured to be 1.24%. The probability of false positives is computed by considering all events with zero hit multiplicity in the off-line analysis and non-zero L0 multiplicity, and is 0.005%.

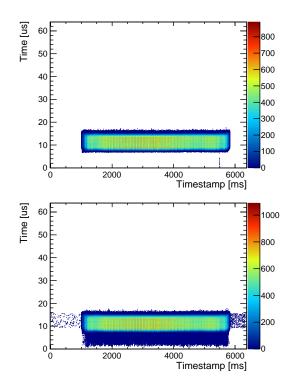

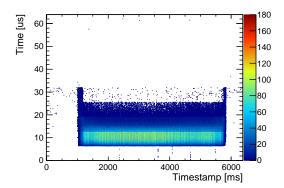

The top plot in fig. 11 displays the 25 ns time slot contained in a L0 trigger primitive versus the generation time of the MTP including such primitive. It can be seen that the firmware latency is very stable, being between

Figure 10: Correlation between the hit multiplicity computed by the RICH L0 firmware and in off-line data analysis.

2 and 3 (6.4  $\mu$ s-long) time frames for the RICH subdetector. The same information for the NA48-CHOD detector is shown in the bottom plot: the latency is lower than in the RICH case, and varies between 1 and 2 time frames, the reason being the 15% higher hit rate in the NA48-CHOD, which reduces the latency of the DM and the DDs.

## 6.2. LAV L0 trigger

The Large Angle Veto (LAV) L0 primitive generator firmware [16] works under the assumption that input digital signals originate from the LAV front-end boards [17]. These boards are double-threshold discriminators producing two digital LVDS output signals from each analogue input signal. Analogue input channels will be referred to as blocks in the following, in analogy with the LAV lead-glass blocks. In 2016-2018 the LAV L0 trigger primitive generator only used information from the 12th LAV station. If information from more LAV stations were to be used, the relevant TEL62 boards could be connected together using InterTELs (section 5.3.1).

The LAV L0 primitive generator starts by associating the low- and high-threshold crossings in a specific block to build hits, and performs a slewing correction on them. The block hits are then clustered together, based on a programmable time interval. A LAV L0 trigger primitive is built from each cluster. The FPGA resource usage for the common logic together with the LAV L0 trigger logic amounts to 79% (28%) of the available logic elements and 51% (39%) of the available memory for the PP- (SL-)FPGA.

Figure 11: Primitive generation delay for the RICH (top) and NA48-CHOD (bottom) sub-detectors.

## 6.2.1. PP-FPGA logic

Fig. 12 shows a scheme of the LAV L0 firmware in the PP-FPGA, whose main task is to generate a *block hit*, if both high and low thresholds are crossed for a block within a programmable time interval. After the times of such hits are corrected for slewing, they are sent to the SL-FPGA.

Figure 12: Block diagram of LAV L0 firmware in the PP-FPGA.

The LAV firmware reads data produced by the HPT-DCs through a FIFO buffer. The input stage reads its content at the rate of 1 word per clock cycle (160 MHz) and sends it to the next firmware module. If the data word is an end-of-frame counter, a global end-of-frame signal is sent to the Event Finder module.

The time-offset and channel mapping module receives data from the input stage continuously. It checks if a word refers to a leading-edge or a trailing-edge time measurement and, if this is the case, it retrieves the proper offset value from the time-offset RAM and the remapped channel number from the mapping RAM and applies them to the current data word. Such memories are fully programmable by the user at configuration time through ECS. The total input-output latency of this module is 4 clock cycles.

The block time is reconstructed by associating the High Threshold (*HT*) and Low Threshold (*LT*) crossing times. For this purpose data are separated into 128 FIFO buffers depending on the channel number by the Channel-Selector module, redirecting data words to the corresponding channel FIFO. Frame timestamp words are sent to all FIFOs in parallel, while leading times are sent only to the proper channel FIFO and trailing times are discarded. At this stage the word size is reduced from 32 to 22 bits, by using a single bit as word type flag (timestamp or leading-edge fine-time), discarding the time bits overlapping between frame timestamp and pulse time, and removing the channel number which is encoded in the FIFO index.

The FIFOs are arranged in 64 blocks, each composed of a *high-threshold FIFO* (HF) and a *low-threshold FIFO* (LF), 16 and 32 words deep respectively, the difference being due to the different rates expected. Each FIFO corresponds to two registers: a 18-bit fine-time register and a 22-bit coarse time register. When a FIFO is not empty, data is read out and stored in these registers, forming a 40-bit output word. If both the HF and LF contain a complete word, *i.e.* both the fine-time and coarse time registers are full, then the block is "ready" to be read-out by the next firmware module.

The Event Finder (EF) module is a FSM which looks for "ready" blocks and builds a block hit. When a block is "ready", the module reads its HT time and stores it, then it reads the LT time and subtracts it from the stored HT time. If the resulting difference matches programmable limits, a block hit is generated, otherwise the earlier of HT and LT is discarded. For each generated block hit the EF produces an output data word with block ID (6 bit), time since the start of the burst (40 bit) and the difference of the HT and LT crossing times, also called rise time (8 bit).

In order to perform a slewing correction, the two threshold values,  $V_{\rm low}$  and  $V_{\rm high}$  set in the LAV frontend boards for every channel, are required. Such values are stored via ECS into the Threshold RAM, with 128 12-bit locations, where the least-significant bit corresponds to 0.1 mV and the maximum value is 409.5 mV. The Slewing Correction module retrieves the appropriate threshold values from the RAM and evaluates the corrected time t by linearly extrapolating the starting point of the analogue signal, based on the measured

threshold-crossing times  $t_{low}$  and  $t_{low}$ . This module is implemented using High Level Synthesis via Catapult<sup>®</sup> [19].

#### 6.2.2. SL-FPGA logic

Fig. 13 illustrates the LAV L0 primitive generating firmware in the SL-FPGA. The firmware collects the block-hits coming from the PP-FPGAs and creates clusters of them according to a programmable time interval. The time of each cluster is calculated by averaging the times of the block hits contained in the cluster. Then, a LAV L0 trigger primitive is generated from each cluster. Finally, the primitives are time-sorted and sent to the MTP assembler module.

Figure 13: Block diagram of the LAV L0 firmware in the SL-FPGA.

The first stage is the Data Merger (DM) module, a FSM handling the 4 input FIFOs containing data coming from each PP-FPGA. The DM reads data from the first non-empty FIFO of all enabled PP-FPGAs; in case two or more FIFOs are not empty at the same time, the priority switches cyclically. The DM produces a global End-of-Frame (EoF) word when it receives an EoF word from each of the enabled PP-FPGAs. Output data from the DM is stored in another FIFO buffer.